www.ti.com

Peripheral Architecture

2.14 Interrupt Support

The DDR2 memory controller supports two addressing modes, linear incrementing and cache line wrap. Upon receipt of an access request for an unsupported addressing mode, the DDR2 memory controller generates an interrupt by setting the LT bit in the interrupt raw register (IRR). The DDR2 memory controller will then treat the request as a linear incrementing request.

This interrupt is called the line trap interrupt and is the only interrupt the DDR2 memory controller supports. It is an

2.15 DMA Event Support

The DDR2 memory controller is a DMA slave peripheral and therefore does not generate DMA events. Data read and write requests may be made directly by masters and by the DMA.

2.16 Power Management

Power dissipation from the DDR2 memory controller may be managed by two methods:

∙

∙Gating input clocks to the module off

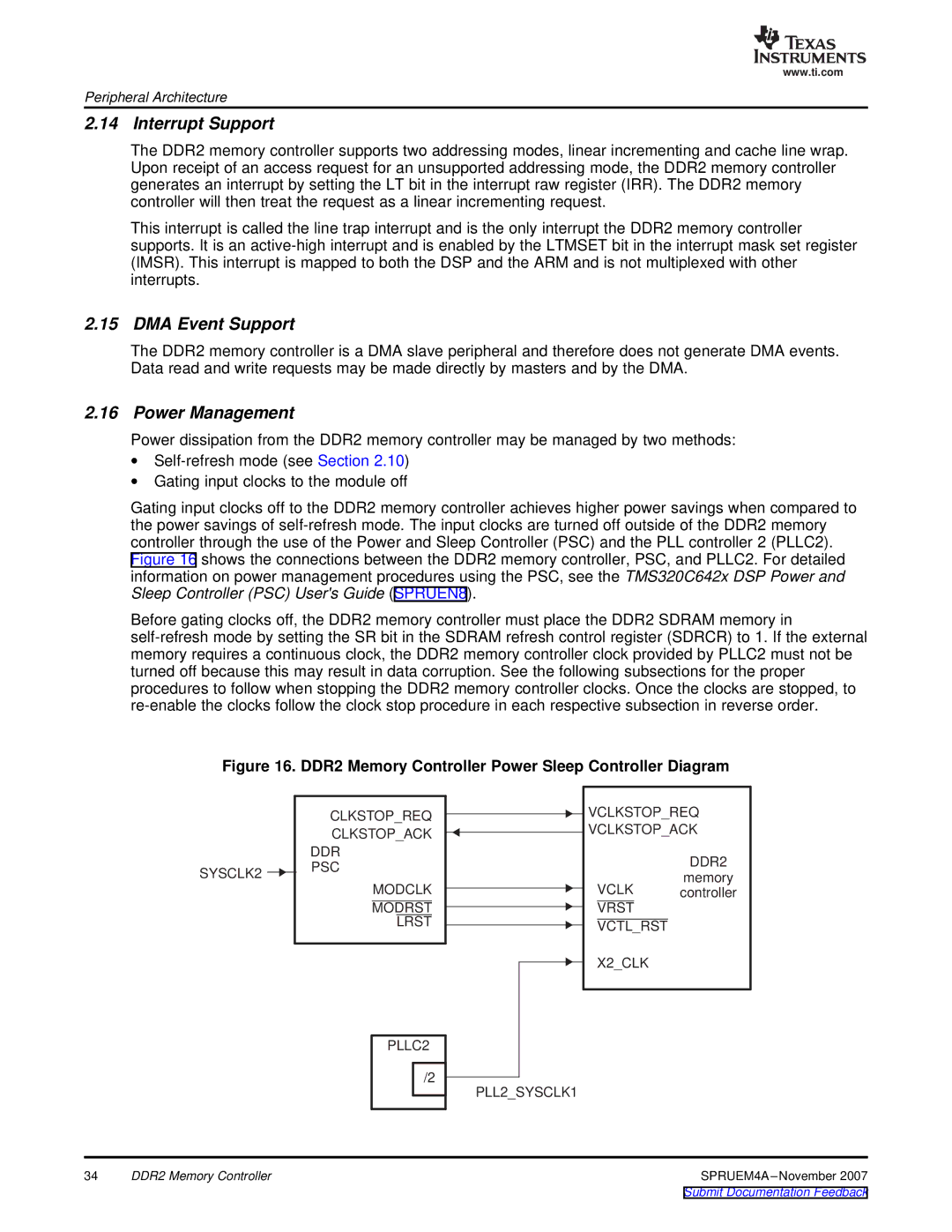

Gating input clocks off to the DDR2 memory controller achieves higher power savings when compared to the power savings of

Before gating clocks off, the DDR2 memory controller must place the DDR2 SDRAM memory in

Figure 16. DDR2 Memory Controller Power Sleep Controller Diagram

CLKSTOP_REQ

CLKSTOP_ACK

|

| DDR |

SYSCLK2 |

| PSC |

|

|

MODCLK

MODRST

LRST

PLLC2

/2

VCLKSTOP_REQ

VCLKSTOP_ACK

DDR2

memory

VCLK controller

VRST

VCTL_RST

X2_CLK

PLL2_SYSCLK1

34 | DDR2 Memory Controller |