www.ti.com

Peripheral Architecture

Once in

2.11 Reset Considerations

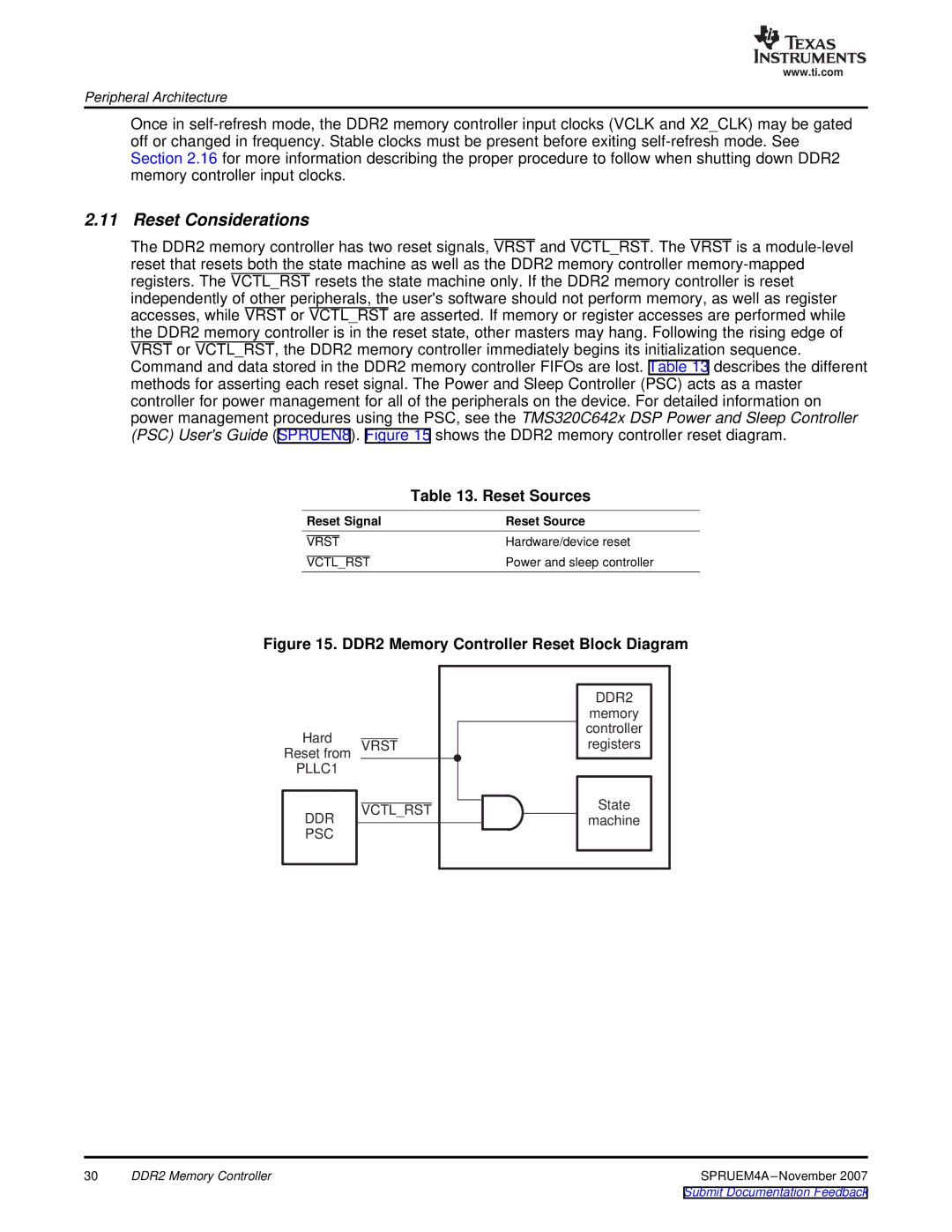

The DDR2 memory controller has two reset signals, VRST and VCTL_RST. The VRST is a

| Table 13. Reset Sources |

Reset Signal | Reset Source |

VRST | Hardware/device reset |

VCTL_RST | Power and sleep controller |

Figure 15. DDR2 Memory Controller Reset Block Diagram

Hard

Reset from

PLLC1

DDR

PSC

VRST

VCTL_RST

DDR2

memory controller registers

State

machine

30 | DDR2 Memory Controller |