www.ti.com

DDR2 Memory Controller Registers

4.5SDRAM Timing Register 2 (SDTIMR2)

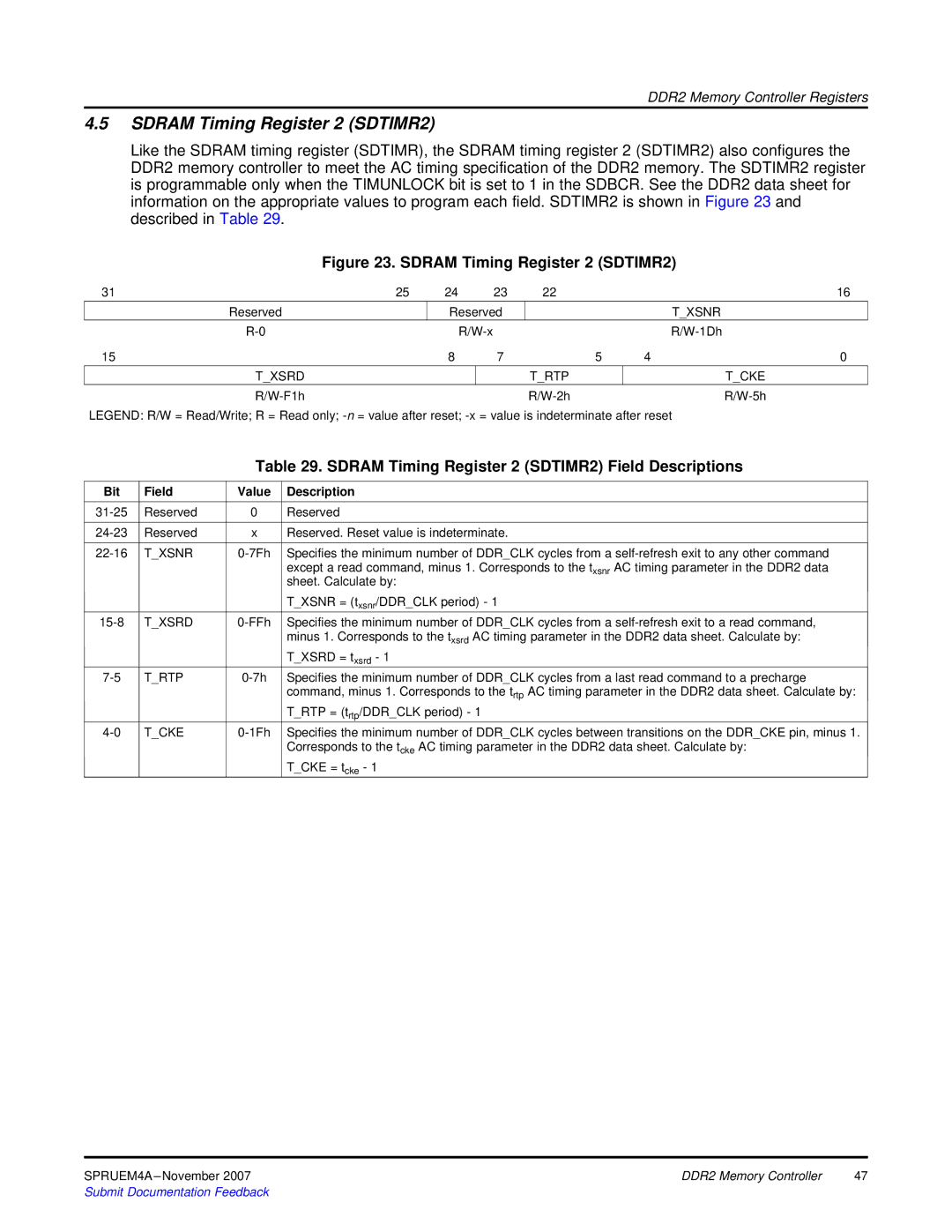

Like the SDRAM timing register (SDTIMR), the SDRAM timing register 2 (SDTIMR2) also configures the DDR2 memory controller to meet the AC timing specification of the DDR2 memory. The SDTIMR2 register is programmable only when the TIMUNLOCK bit is set to 1 in the SDBCR. See the DDR2 data sheet for information on the appropriate values to program each field. SDTIMR2 is shown in Figure 23 and described in Table 29.

Figure 23. SDRAM Timing Register 2 (SDTIMR2)

31 | 25 | 24 | 23 | 22 |

| 16 |

Reserved |

| Reserved |

|

| T_XSNR | |

|

|

|

| |||

15 |

| 8 | 7 | 5 | 4 | 0 |

T_XSRD |

|

|

| T_RTP |

| T_CKE |

|

|

|

| |||

LEGEND: R/W = Read/Write; R = Read only;

Table 29. SDRAM Timing Register 2 (SDTIMR2) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

Reserved | x | Reserved. Reset value is indeterminate. | |

T_XSNR | Specifies the minimum number of DDR_CLK cycles from a | ||

|

|

| except a read command, minus 1. Corresponds to the txsnr AC timing parameter in the DDR2 data |

|

|

| sheet. Calculate by: |

|

|

| T_XSNR = (txsnr/DDR_CLK period) - 1 |

T_XSRD | Specifies the minimum number of DDR_CLK cycles from a | ||

|

|

| minus 1. Corresponds to the txsrd AC timing parameter in the DDR2 data sheet. Calculate by: |

|

|

| T_XSRD = txsrd - 1 |

T_RTP | Specifies the minimum number of DDR_CLK cycles from a last read command to a precharge | ||

|

|

| command, minus 1. Corresponds to the trtp AC timing parameter in the DDR2 data sheet. Calculate by: |

|

|

| T_RTP = (trtp/DDR_CLK period) - 1 |

T_CKE | Specifies the minimum number of DDR_CLK cycles between transitions on the DDR_CKE pin, minus 1. | ||

|

|

| Corresponds to the tcke AC timing parameter in the DDR2 data sheet. Calculate by: |

![]() T_CKE = tcke - 1

T_CKE = tcke - 1

DDR2 Memory Controller | 47 | |

Submit Documentation Feedback |

|

|