www.ti.com

DDR2 Memory Controller Registers

4.12 VTP IO Control Register (VTPIOCR)

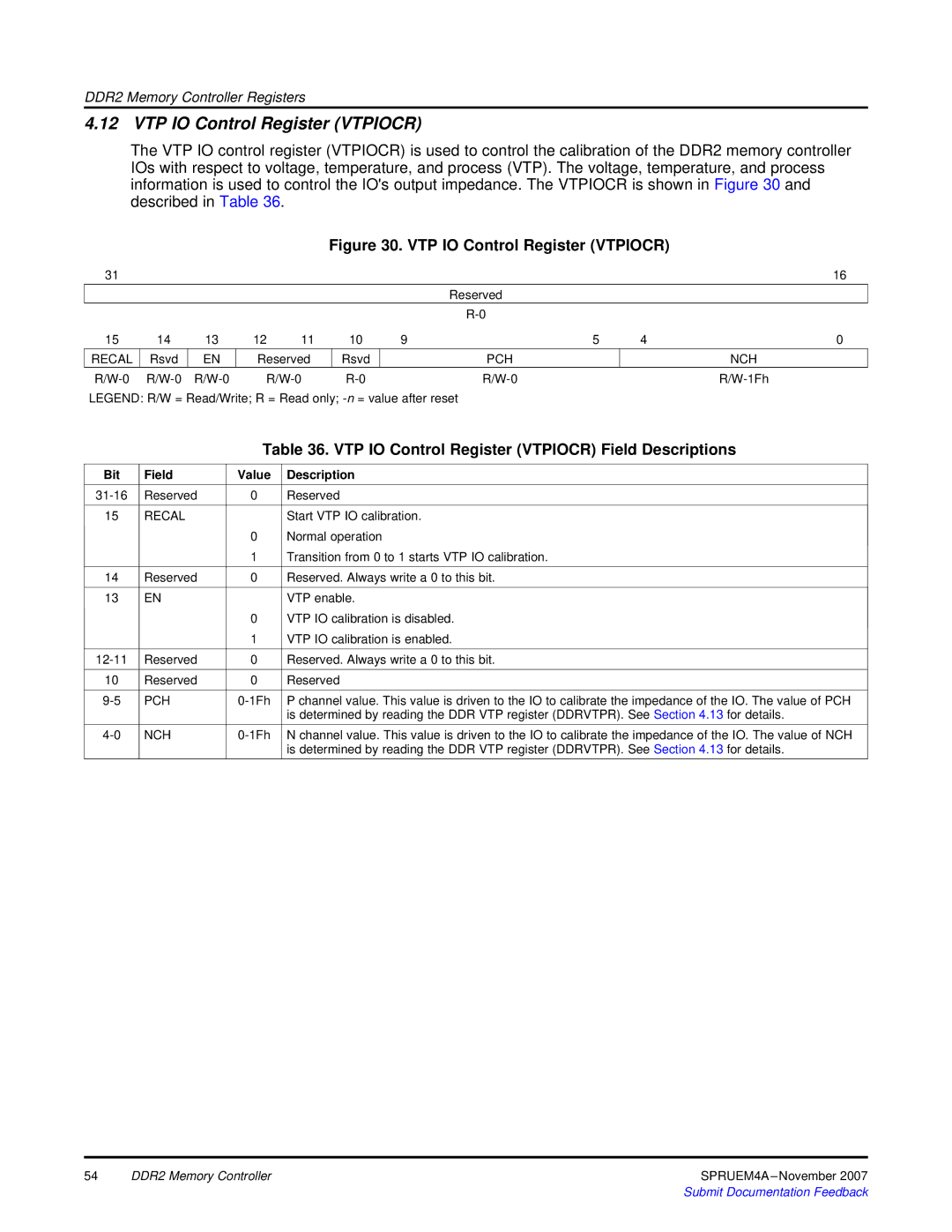

The VTP IO control register (VTPIOCR) is used to control the calibration of the DDR2 memory controller IOs with respect to voltage, temperature, and process (VTP). The voltage, temperature, and process information is used to control the IO's output impedance. The VTPIOCR is shown in Figure 30 and described in Table 36.

Figure 30. VTP IO Control Register (VTPIOCR)

31 |

|

|

|

|

|

|

|

| 16 |

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

|

|

|

|

|

| |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 5 | 4 | 0 |

RECAL | Rsvd | EN | Reserved | Rsvd | PCH |

|

| NCH | |

|

| ||||||||

LEGEND: R/W = Read/Write; R = Read only;

Table 36. VTP IO Control Register (VTPIOCR) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

15 | RECAL |

| Start VTP IO calibration. |

|

| 0 | Normal operation |

|

| 1 | Transition from 0 to 1 starts VTP IO calibration. |

14 | Reserved | 0 | Reserved. Always write a 0 to this bit. |

13 | EN |

| VTP enable. |

|

| 0 | VTP IO calibration is disabled. |

|

| 1 | VTP IO calibration is enabled. |

Reserved | 0 | Reserved. Always write a 0 to this bit. | |

10 | Reserved | 0 | Reserved |

PCH | P channel value. This value is driven to the IO to calibrate the impedance of the IO. The value of PCH | ||

|

|

| is determined by reading the DDR VTP register (DDRVTPR). See Section 4.13 for details. |

NCH | N channel value. This value is driven to the IO to calibrate the impedance of the IO. The value of NCH | ||

|

|

| is determined by reading the DDR VTP register (DDRVTPR). See Section 4.13 for details. |

54 | DDR2 Memory Controller |