www.ti.com

DDR2 Memory Controller Registers

4.6Peripheral Bus Burst Priority Register (PBBPR)

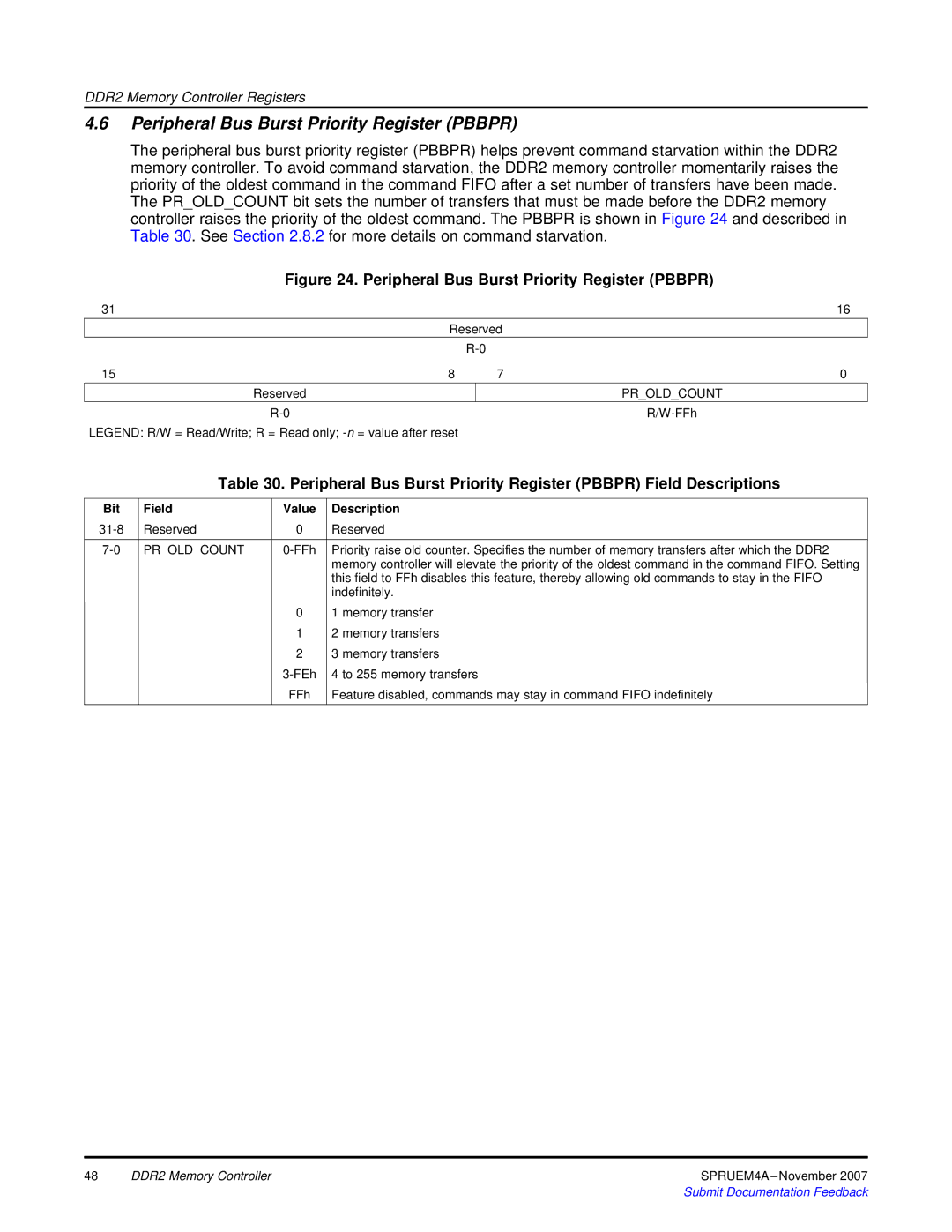

The peripheral bus burst priority register (PBBPR) helps prevent command starvation within the DDR2 memory controller. To avoid command starvation, the DDR2 memory controller momentarily raises the priority of the oldest command in the command FIFO after a set number of transfers have been made. The PR_OLD_COUNT bit sets the number of transfers that must be made before the DDR2 memory controller raises the priority of the oldest command. The PBBPR is shown in Figure 24 and described in Table 30. See Section 2.8.2 for more details on command starvation.

Figure 24. Peripheral Bus Burst Priority Register (PBBPR)

31 |

|

| 16 |

| Reserved |

| |

|

|

| |

15 | 8 | 7 | 0 |

Reserved |

|

| PR_OLD_COUNT |

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 30. Peripheral Bus Burst Priority Register (PBBPR) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

PR_OLD_COUNT | Priority raise old counter. Specifies the number of memory transfers after which the DDR2 | ||

|

|

| memory controller will elevate the priority of the oldest command in the command FIFO. Setting |

|

|

| this field to FFh disables this feature, thereby allowing old commands to stay in the FIFO |

|

|

| indefinitely. |

|

| 0 | 1 memory transfer |

|

| 1 | 2 memory transfers |

|

| 2 | 3 memory transfers |

|

| 4 to 255 memory transfers | |

|

| FFh | Feature disabled, commands may stay in command FIFO indefinitely |

48 | DDR2 Memory Controller |