Agilent Technologies

Warn in G

WA R N I N G

Japan 0120 421 0120 421 678 FAX Mexico 5081

Agilent Technologies Sales and Service Offices

Conventions used in this Manual

Structure of this Manual

This manual is divided into 5 parts

T E

Related Manuals

Table of Contents

Signal Conditioning

Specific Command Summary

Root Layer Command

Signal Generation The SOURce Subsystem

Error Handling

Installing the Agilent 816x Instrument Driver

Using Visual Programming Environments

Features of the Agilent 816x Instrument Driver

Obsolete Commands

Compatibility Issues

Preset Defaults

Removed Command

Agilent 8163A/B, 8164A/B & 8166A/B Mainframes, Sixth Edition

Operational/Questionable Status System for

Agilent 8163A/B, 8164A/B & 8166A/B Mainframes, Sixth Edition

List of Tables

Agilent 8163A/B, 8164A/B & 8166A/B Mainframes, Sixth Edition

Introduction to Programming

Scpi Consortium Office Bode Enterprise

Gpib Interface

Camino del Rio South, Suite 340 San Diego, CA

Introduction to Programming

Mnemonic Function

Returning the Instrument to Local Control

If the instrument is in remote control, a screen resembling

Gpib Interface

Message Queues

Message Queues

Clearing the Input Queue

How the Input Queue Works

Output Queue

Is placed as the last message in the queue

Error Queue

If no error has occurred, the error queue contains

If more than 29 errors are put into the queue, the message

Programming and Syntax Diagram Conventions

Command message is ended by a line feed character LF or

Crlf

Statoperenab

Statusoperationenable

Short Form and Long Form

Is in long form Short form of this message is

String Value Wsp

Command and Query Syntax

Unit Default Allowed Mnemonics

Units

Slot and Channel Numbers

Data Types

Laser Selection Numbers

112,

Input to your Return Loss module for the following commands

Common Commands

Common Commands

Gives a summary of the common commands

Common Command Summary

Parameter Function

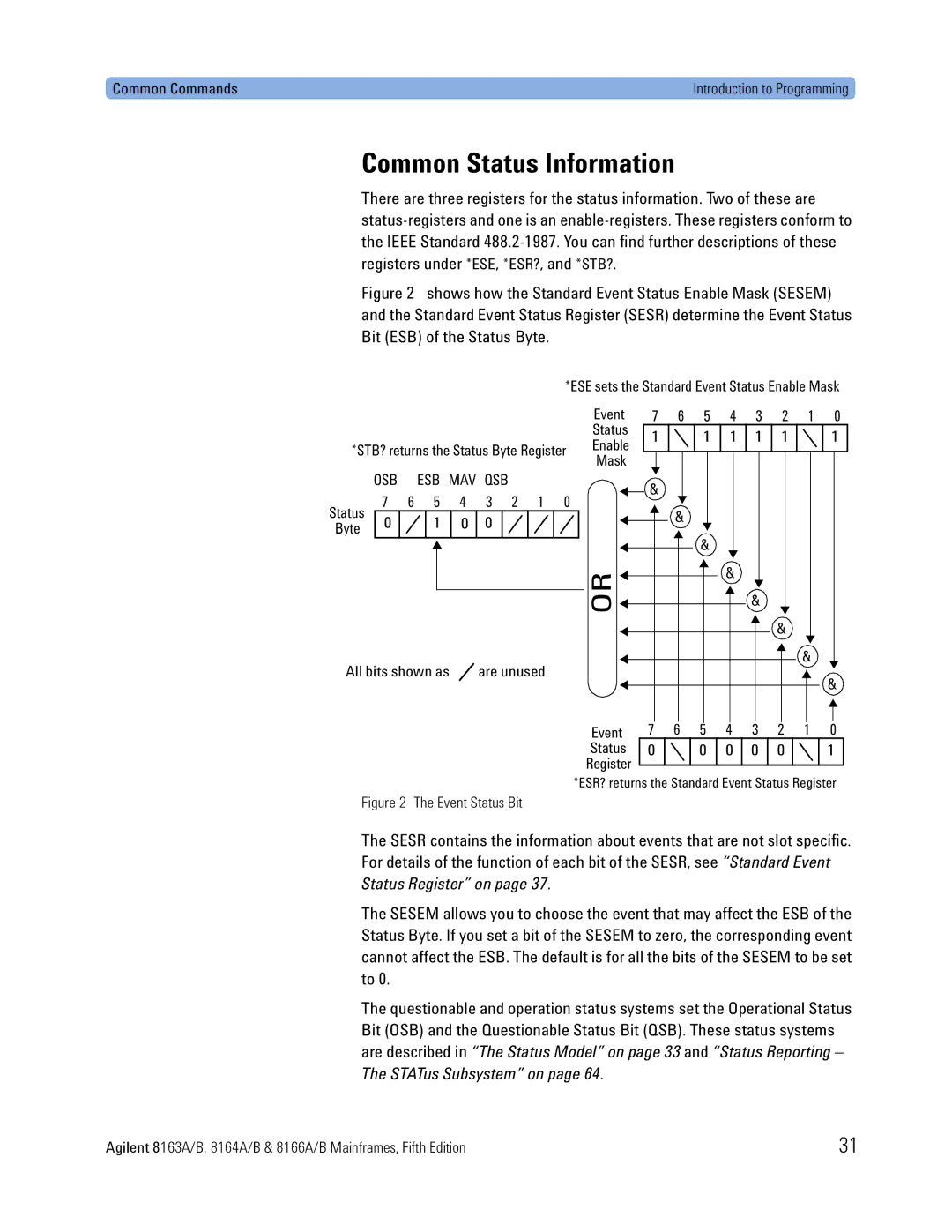

All bits shown as are unused Event Status Enable Mask

ESE sets the Standard Event Status Enable Mask

Common Status Information

T E

Status Registers

Status Model

Status Model

Slot Status Event

Status System for 8163A/B & 8164A/B

Slot Status Condition

Status System for 8166A/B

Operation/Questionable Status Summary

Annotations

Status Byte Register

Standard Event Status Register

Questionable Slot Status Register

Operation/Questionable Status Summary Register

Operation/Questionable Slot Status

Operation Slot Status Register

Status Model

Long

Status Command Summary

OPT? WAI IDN?

Other Commands

Introduction to Programming

Specific Commands

WAVelengthREFerence/?

Specific Command Summary

Specific Commands

Command Description

INPUTnCHANnelm

Command Description DISPlay

FETChnCHANnelmSCALar

INITiatenCHANnelm

ROUTen

PATH/?

Terminals

READnCHANnelm

SENSenCHANnelmFUNCtion

SENSenCHANnelmPOWer

SLOTn

Command Description SENSenCHANnelmPOWerReference

SENSenCHANnelmRETurnlossCALibration

SENSenCHANnelmRETurnlossCORRection

SOURcenCHANnelmAM

SOURcenCHANnelmPOWer

SOURcenCHANnelmPOWerATTenuationl

SOURcenCHANnelm

SOURcenCHANnelmWAVelengthREFerence

SOURcenCHANnelmWAVelengthCORRection

SOURcenCHANnelmWAVelengthSWEepSTEP

Command Description SOURcenCHANnelmWAVelengthSWEep

STATusnOPERation

Command Description SPECial

STATusn

STATusOPERation

SYSTemCOMMunicateGPIB

Command Description STATusnQUEStionable

Slot n

SYSTem

Specific Commands

Instrument Setup and Status

Instrument Setup and Status

IEEE-Common Commands

Status byte register STB

Error queue

At power-on By sending a value of zero

Standard event status register Sesr

Bit Mnemonic Decimal Value

ESE?

Agilent Technologies Manufacturer

Complete, Command Idle State

Power-on

Parameters None Response Identification terminated by END

Example OPT? → 81682A , , 81533B, 81532A, END

Plete, Command Idle State

Lead to useful gains in program execution efficiency

Slot 1 for the Agilent 8163A/B and Agilent 8166A/B

Following are not changed

Error queue

Selftest failed on Mainframe

Bits Mnemonic

Pending operations, are completed during the wait period

WAI

Agilent 8163A/B Agilent 8164A/B Agilent 8166A/B

Status Reporting The STATus Subsystem

STATusOPERationEVENtLEVel0?

Bits Mnemonics

STATusOPERationCONDitionLEVel0?

Status Reporting The STATus Subsystem

Bits Mnemonics Decimal Value Agilent 8166A/B

STATusOPERationENABleLEVel

STATusOPERationENABleLEVel0?

STATusOPERationEVENtLEVel1?

STATusOPERationCONDitionLEVel1?

STATusOPERationENABleLEVel1

Syntax STATusOPERationENABleLEVel1wspvalue Description

STATusOPERationENABleLEVel1?

STATus nOPERationCONDition?

Offset

Extrapolated values

STATus nOPERationEVENt?

STATusPRESet

STATusnOPERationENABle

STATusnOPERationENABlewspvalue

STATusnOPERationENABle?

Agilent 8163A/B Agilent 8164A/B

STATusQUEStionableEVENtLEVel0?

Statques? → +0END

STATusQUEStionableCONDitionLEVel0?

STATusQUEStionableENABleLEVel0?

STATusQUEStionableENABleLEVel

STATusQUEStionableEVENtLEVel1?

Syntax STATusQUEStionableCONDitionLEVel 1? Description

Syntax STATusQUEStionableENABleLEVel 1wspvalue Description

STATusQUEStionableENABleLEVel1?

STATusQUEStionableCONDitionLEVel 1?

STATusnQUEStionableCONDition?

STATusnQUEStionableEVENt?

Syntax STATusnQUEStionableEVENt? Description

11-15 Not Used

STATusnQUEStionableENABlewspvalue

STATusnQUEStionableENABle

STATusnQUEStionableENABle?

SYSTemDATE

SYSTemERRor?

SYSTemDATE?

Backlight and contrast of the display

Output and error queues

Standard Event Status Enable Mask SESEM,

Gpib interface state

Systcommgpibaddr

SYSTemTIME?

SYSTemVERSion?

SYSTemCOMMunicateGPIBSELFADDRess

Measurement Operations & Settings

Measurement Operations & Settings

Root Layer Command

LOCK?

Slot nIDN?

Agilent Technologies as the manufacturer

Manufacturer

Slot nEMPTy?

SLOTnHEADnEMPTy?

SLOTnTST?

SLOTnHEADnIDN?

Syntax SLOTnHEADmWAVelengthRESPonse? Description

SLOTnHEADmOPTions?

SLOTnHEADmTST?

SLOTnHEADmWAVelengthRESPonse?

SLOTnHEADmWAVelengthRESPonseCSV?

SPECialREBoot

SLOTnHEADmWAVelengthRESPonseSIZE?

Measurement Functions The SENSe Subsystem

Command

Measurement Functions SENSe Subsystem

Agilent 81635A and Agilent 81619A Master Slave Channels

SENSenCHANnelmPOWerUNIT/? SENSenCHANnelmPOWerWAVelength/?

FETChnCHANnelmSCAlarRETurnloss?

FETChnCHANnelmSCAlarPOWerDC?

INITiatenCHANnelmIMMediate

FETChnCHANnelmSCAlarMONitor?

INITiatenCHANnelmCONTinuous

INITiate nCHANnel mCONTinuous?

Read nCHANnel mSCALarPOWerALL?

Member of the pair represents the channel number

Read nCHANnel mPOWerALLCONFig?

READnCHANnelmSCALarPOWerDC?

Ber

READnCHANnelmSCALarRETurnloss?

READnCHANnelmSCALarMONitor?

SENSenCHANnelmCORRectionLOSSINPutMAGNitude?

SENSe nCHANnel mCORRectionLOSSINPutMAGNitude

SENSenCHANnelmCORRectionCOLLectZERO

Operation

SENSe nCHANnel mCORRectionCOLLectZERO?

SENSenCHANnelmCORRectionCOLLectZEROALL

Averaging Time

SENSenCHANnelmFUNCtionPARameterLOGGing

SENSenCHANnelmFUNCtionPARameterLOGGing?

Wind

SENSenCHANnelmFUNCtionPARameterMINMax

SENSenCHANnelmFUNCtionPARameterMINMax?

Cont

Response Example Affects Dual sensors

SENSenCHANnelmFUNCtionPARameterSTABility

Period time

Averaging Time Period Time

Return Loss modules

SENSenCHANnelmFUNCtionPARameterSTABility?

SENSenCHANnelmFUNCtionRESult?

Sens1funcres? →

SENSe nCHANnel mFUNCtionRESultMAXBlocksize?

SENSe nCHANnel mFUNCtionRESultBLOCk?

SENSenCHANnelmFUNCtionRESultMONitor?

SENSenCHANnelmFUNCtionSTATe

100

SENSenCHANnelmFUNCtionSTATe?

SENSenCHANnelmFUNCtionTHReshold?

SENSenCHANnelmPOWerATIMe

101

SENSenCHANnelmFUNCtionTHReshold

102

SENSenCHANnelmPOWerATIMe?

SENSenCHANnelmPOWerRANGeUPPer

Range Upper Linear Power Limit

Range Upper Linear

SENSenCHANnelmPOWerRANGeUPPer?

SENSenCHANnelmPOWerRANGeMONitorUPPer

103

SENSenCHANnelmPOWerRANGeAUTO?

SENSenCHANnelmPOWerRANGeMONitorUPPer?

SENSenCHANnelmPOWerRANGeAUTO

Ment. Otherwise, it must be set by the sensnpowrang command

DB if you use TOMODule or

Reference mode using the command

105

You must append a unit type

106

SENSenCHANnelmPOWerREFerenceDISPlay

SENSenCHANnelmPOWerREFerenceSTATe

SENSenCHANnelmPOWerREFerenceSTATe?

To the channel for the second value

SENSe nCHANnel mPOWerREFerenceSTATeRATio

SENSenCHANnelmPOWerREFerenceSTATeRATio?

107

108

SENSe nCHANnel mPOWerUNIT

SENSenCHANnelmPOWerUNIT?

SENSenCHANnelmPOWerWAVelength

SENSenCHANnelmRETurnlossCALibrationFACTory

SENSenCHANnelmPOWerWAVelength?

109

SENSenCHANnelmRETurnlossCALibrationFACTory

SENSe nCHANnel mRETurnlossCALibrationTERMination?

110

SENSe nCHANnel mRETurnlossCALibrationCOLLectTERMination

Defined termination reference measurement. See

SENSenCHANnelmRETurnlossCORRectionFPDeltal

111

SENSenCHANnelmRETurnlossCORRectionFPDeltal?

Lower wavelength source is denoted by

112

SENSe nCHANnel mRETurnlossCORRectionREFLectance l

DB reference

OUTPutnCHANnelmCONNection?

Signal Generation The SOURce Subsystem

113

OUTPutnCHANnelmCONNection

OUTPutnCHANnelmPATH?

114

OUTPutnCHANnelmSTATe

SOURcenCHANnelmAMINTernalFREQuencyl

115

SOURcenCHANnelmAMINTernalFREQuencyl?

INTINT1INT2COHCAEXTEXTDEXTWVLLBACK012356

116

SOURcenCHANnelmAMSOURcel

Syntax SOURcenCHANnelmAMSOURcelwsp

Wavelength source is denoted by

117

SOURcenCHANnelmAMSTATel

SOURcenCHANnelmAMSTATel?

SOURcenCHANnelmFMSOURcel

118

SOURce nCHANnel mAMCOHCtrlCOHLevel l

SOURcenCHANnelmAMCOHCtrlCOHLevell?

SOURcenCHANnelmFMSTATel?

119

SOURce nCHANnel mFMSOURce l?

SOURcenCHANnelmFMSTATel

SOURcenCHANnelmFMSBSCtrlFREQuencyl?

120

SOURcenCHANnelmFMSBSCtrlFREQuencyl

Mhzkhzhzminmaxdef

SOURcenCHANnelmMODout?

121

SOURcenCHANnelmFMSBSCtrlLevell?

SOURcenCHANnelmMODout

122

SOURcenCHANnelmPOWerATTenuationl?

This command is available in Attenuation Mode Only

SOURcenCHANnelmPOWerATTenuationlAUTO

SOURcenCHANnelmPOWerATTenuationlAUTO?

SOURcenCHANnelmPOWerATTenuationlDARK

SOURcenCHANnelmPOWerLEVelIMMediateAMPLitudel

SOURcenCHANnelmPOWerATTenuationlDARK?

124

125

SOURcenCHANnelmPOWerLEVelIMMediateAMPLitudel?

Also allowed MIN minimum amplitude level

SOURcenCHANnelmPOWerLEVelRISetimel?

SOURcenCHANnelmPOWerLEVelRISetimel

126

SOURcenCHANnelmPOWerUNIT?

SOURce nCHANnel mPOWerSTATe

SOURcenCHANnelmPOWerSTATe?

SOURcenCHANnelmPOWerUNIT

SOURcenCHANnelmPOWerWAVelength?

SOURcenCHANnelmPOWerWAVelength

128

SOURce nCHANnel mREADoutDATABLOCk?

129

SOURce nCHANnel mREADoutDATA?

Pmax

SOURcenCHANnelmWAVelengthCWlFIXEDl

130

SOURcenCHANnelmWAVelengthCWlFIXEDlwspvalue

SOURcenCHANnelmREADoutPOINts?

SOURcenCHANnelmWAVelengthCWlFIXEDl?

131

SOURcenCHANnelmWAVelengthCORRectionARA

81989A, 81949A

132

SOURce nCHANnel mWAVelengthCORRectionARAALL

SOURce nCHANnel mWAVelengthCORRectionAUTocalib

SOURce nCHANnel mWAVelengthCORRectionZERO

133

SOURcenCHANnelmWAVelengthCORRectionZEROALL

Thzghzmhzkhzhz

134

SOURcenCHANnelmWAVelengthCORRectionZEROAUTO

SOURcenCHANnelmWAVelengthFREQuencyl

SOURcenCHANnelmWAVelengthREFerenceDISPlay

135

SOURcenCHANnelmWAVelengthFREQuencyl?

SOURcenCHANnelmWAVelengthREFerencel?

SOURcenCHANnelmWAVelengthSWEepCHECkparams?

136

Message

SOURce nCHANnel mWAVelengthSWEepCYCLes?

137

ValueMINMAXDEF0

SOURce nCHANnel mWAVelengthSWEepCYCLes

SOURcenCHANnelmWAVelengthSWEepEXPectedtriggers?

138

SOURce nCHANnel mWAVelengthSWEepDWELl

SOURce nCHANnel mWAVelengthSWEepDWELl?

Start Sweep waiting for trigger Trigger →

139

SOURcenCHANnelmWAVelengthSWEepFLAG?

Sweep state

SOURcenCHANnelmWAVelengthSWEepLLOGgingwspOFFON01

Following settings are the prerequisites for Lambda Logging

140

SOURcenCHANnelmWAVelengthSWEepLLOGging

SOURcenCHANnelmWAVelengthSWEepPMAX?

141

SOURcenCHANnelmWAVelengthSWEepMODE

SOURcenCHANnelmWAVelengthSWEepMODE?

SOURcenCHANnelmWAVelengthSWEepREPeat

142

SOURcenCHANnelmWAVelengthSWEepREPeat?

SOURcenCHANnelmWAVelengthSWEepSPEed?

143

SOURce nCHANnel mWAVelengthSWEepSOFTtrigger

SOURcenCHANnelmWAVelengthSWEepSPEed

SOURcenCHANnelmWAVelengthSWEepSTOP

144

SOURce nCHANnel mWAVelengthSWEepSTARt

SOURcenCHANnelmWAVelengthSWEepSTARt?

SOURcenCHANnelmWAVelengthSWEepSTATe

If you enable lambda logging see

145

SOURcenCHANnelmWAVelengthSWEepSTOP?

SOURcenCHANnelmWAVelengthSWEepSTEPPREVious

146

SOURcenCHANnelmWAVelengthSWEepSTATe?

SOURcenCHANnelmWAVelengthSWEepSTEPNEXT

SOURce nCHANnel mWAVelengthSWEepSTEPWIDTh?

147

INPut nCHANnel mATTenuation

Signal Conditioning

INPut and OUTput commands

148

INPutnCHANnelmOFFSetDISPlay

149

INPutnCHANnelmOFFSet

INPutnCHANnelmOFFSet?

INPutnCHANnelmATTenuationSPEed?

INPutnCHANnelmOFFSetPOWermeter

150

INPutnCHANnelmATTenuationSPEed

INPutnCHANnelmWAVelength?

151

INPutnCHANnelmWAVelength

MAX DEF

OUTPut nCHANnel mAPMode?

OUTPutnCHANnelmPOWer

OUTPutnCHANnelmPOWer?

152

153

OUTPutnCHANnelmPOWerREFerence

OUTPutnCHANnelmPOWerREFerence?

OUTPutnCHANnelmPOWerREFerencePOWermeter

154

OUTPutnCHANnelmPOWerOFFSet

OUTPutnCHANnelmPOWerOFFSet?

OUTPutnCHANnelmPOWerOFFSetPOWermeter

155

OUTPut nCHANnel mPOWerCONTRol

OUTPutnCHANnelmPOWerCONTRol?

OUTPutnCHANnelmPOWerUNit

OUTPut nCHANnel mSTATe

OUTPut nCHANnel mPOWerUNit?

OUTPutnCHANnelmSTATeAPOWeron

156

OUTPutnCHANnelmATIMe?

OUTPutnCHANnelmSTATeAPOWeron?

157

OUTPutnCHANnelmATIMe

OUTPutnCHANnelmCORRectionCOLLectionZEROALL

158

OUTPCORRCOLLZER0? → 0END

159

Table of wavelength-dependent offsets

CONF1OFFSWAVSTAT on

CONFigurenCHANnelmOFFSetWAVelengthSTATe

CONFigurenCHANnelmOFFSetWAVelengthSTATe?

160

CONF1OFFSWAVREF 4,2

CONFigurenCHANnelmOFFSetWAVelengthVALue

CONFigurenCHANnelmOFFSetWAVelengthREFerence

161

162

CONFigurenCHANnelmOFFSetWAVelengthREFerence?

CONFigurenCHANnelmOFFSetWAVelengthVALueWAVelength?

CONFigurenCHANnelmOFFSetWAVelengthVALueOFFSet?

163

CONFigurenCHANnelmOFFSetWAVelengthVALuePAIR?

CONFigurenCHANnelmOFFSetWAVelengthVALueDELete

CONFigurenCHANnelmOFFSetWAVelengthVALueDELeteALL

CONF1OFFSWAVTABSIZE? →

CONFigurenCHANnelmOFFSetWAVelengthTABle?

CONFigurenCHANnelmOFFSetWAVelengthTABleSIZE?

164

165

When the attenuator is hosted in Slot

TIP Query the Scpi error queue using SYSTERR?

Slot Numbers

166

Command Semantic

Ieee Commands

Display and System Commands

167

User Calibration Data

Status Commands

168

ROUTe nCHANnel m

Signal Routing

Switch modules

169

170

ROUTenCHANnelmCONFig?

Syntax ROUTenCHANnelmCONFig? Description

ROUTenCHANnelmCONFigROUTe?

Software Triggering Data Acquisition Functions Sensfuncstat

Triggering The TRIGger Subsystem

171

Hardware

Software Triggering Data Acquisition Functions

Generating Output Triggers from Power Measurements

DISabled An output trigger will never be generated AVGover

172

173

TRIGgernCHANnelmINPut?

174

TRIGgernCHANnelmINPutREARm

TRIGgernCHANnelmOFFSet value

175

TRIGger nCHANnel mINPutREARm?

TRIGgernCHANnelmOFFSet

Continuous mode, wavswestepwidt is used for triggering, see

176

TRIGger nCHANnel mOUTPut

Return loss modules

TRIGger nCHANnel mOUTPutREARm

Output triggers using power measurements

TRIGgerCONFiguration

177

178

TRIGgerCONFiguration?

TRIGgerCONFigurationFPEDal

TRIGgerCONFigurationFPEDal?

Bit unsigned integer , see below

Extended Trigger Configuration

179

TRIGger

180

Extended Trigger Configuration

Node B Input Configuration

Node a Input Configuration

181

182

Extended Trigger Configuration Example

Output Trigger Connector or Individual module slots

Output Matrix Configuration

Trigconfext #H2,#H0,#H0 is described by -1 and sets one bit

183

Sequence starts again at and continues until the sweep ends

184

185

Mass Storage, Display, and Print Functions

Display

Display Operations

DISPlay Subsystem

186

DISPlayBRIGhtness?

DISPlayENABle

DISPlayENABle?

187

Mass Storage, Display, and Print Functions

188

DISPlayLOCKout?

CD-ROM 08164-90BC4

Instrument using Visa library calls

189

Same program

190

How to Use Visa Calls

Visa Programming Examples

191

How to Use Visa Calls

192

How to Set up a Fixed Laser Source

193

How to Set up a Fixed Laser Source

194

How to Measure Power using FETCh and Read

How to Measure Power using FETCh and Read

195

196

197

198

How to Co-ordinate Two Modules

How to Co-ordinate Two Modules

199

200

201

202

How Power Varies with Wavelength

How Power Varies with Wavelength

203

204

205

206

How to Log Results

How to Log Results

207

208

209

210

211

212

213

Agilent 816x VXIplug&play Instrument Driver

Agilent 816x VXIplug&play Instrument Driver

214

215

Installing the Agilent 816x Instrument Driver

216

Program Folder Item Options

217

218

Using Visual Programming Environments

Getting Started with Agilent VEE

Gpib Interfacing in Agilent VEE

Select hp816X from the Plug&play Driver Name drop-down list

Using Visual Programming Environments

219

Enter the following information Name enter hp816X

220

221

Getting Started with LabView

This folder contains a subfolder named instr.lib

FP Conversion Options Box

222

LabView is a trademark of National Instruments Corporation

223

Instrument Driver with LabView

224

Getting Started with LabWindows

Features of the Agilent 816x Instrument Driver

Features of the Agilent Instrument Driver

225

226

Directory Structure

Opening an Instrument Session

Opening an Instrument Session

227

Successful completion of this function returns Visuccess

228

Closing an Instrument Session

Visa Data Types and Selected Constant Definitions

229

ViStatus errStatus

Error Handling

Check for an error or event after each function

230

231

Error Handling

Development Environments

Introduction to Programming

Example Programs

VISA-Specific Information

233

Microsoft Visual Basic 4.0 or higher

Agilent VEE 5.01 or higher

LabWindows CVI/ R 4.0 or higher

234

Online Information

Latest copy of this driver can be downloaded via

235

Lambda Scan Applications

Lambda Scan Applications

236

Equally Spaced Datapoints

Prepare Lambda Scan Function

How to Perform a Lambda Scan Application

237

Get Lambda Scan Parameters

Get Lambda Scan Parameters Function

Execute Lambda Scan Function

238

239

How to Perform a Multi-Frame Lambda Scan Application

8164A or B Power

Power 8163A or B

240

Equally Spaced Datapoints Function

Register Mainframe Function

Unregister Mainframe Function

241

Prepare Multi Frame Lambda Scan Function

242

Get MF Lambda Scan Parameters Function

Execute Multi Frame Lambda Scan Function

Get Lambda Scan Result Function

Maximum number of channels that may be specified is

Get Number of PWM Channels Function

Get Channel Location Function

243

244

257

Error Codes

258

Gpib Error Strings

Program mnemonic too long

259

Suffix too long

260

New 201

261

New 185

Standard 200

Old 213

262

Old 211

Old 212

Old 221

263

Standard 222

264

265

266

267

268

To -499 Query Errors

Standard 440

269

Standard 420

Standard 430

Overview for Unsupported Strings

270

245

Gpib Command Compatibility List

Gpib Bus Compatibility

Compatibility Issues

These commands are incompatible

Command Change Affects

247

Preset defaults are different

Preset Defaults

248

249

Removed Command

Old Command New Command Affects

Obsolete Commands

250

Dispbrig

Changed Parameter Syntax Semantics

251

SOURAMFREQ/?

SENSPOWUNIT?

Changed Query Result Values

252

TST

Change Affects

Timing Behavior

253

Details the ways in which timing behavior is different

Returned Value Affects

254

FLT/DBLMAX

Command Order

Command Order

255

256

Instrument Status Settings

271

Index

Slot

272

Page

Agilent Technologies, Deutschland GmbH 08164-90B64