FIFO Mode |

|

|

|

| Programming | |

|

|

|

|

|

| |

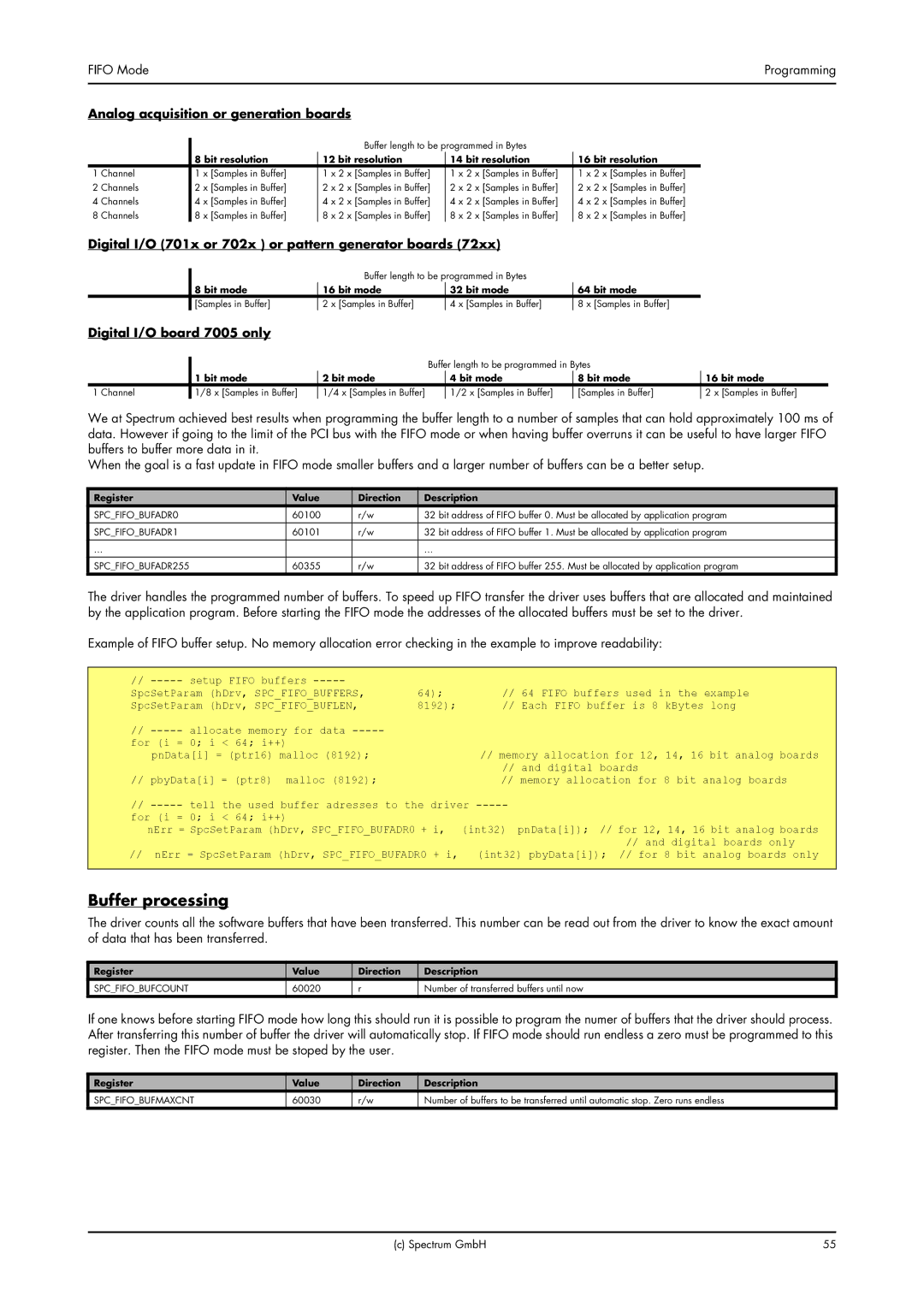

Analog acquisition or generation boards |

|

|

| |||

|

|

| Buffer length to be programmed in Bytes |

|

| |

|

|

|

|

| ||

|

| 8 bit resolution | 12 bit resolution | 14 bit resolution | 16 bit resolution | |

1 | Channel | 1 x [Samples in Buffer] | 1 x 2 x [Samples in Buffer] | 1 x 2 x [Samples in Buffer] | 1 x 2 x [Samples in Buffer] |

|

2 | Channels | 2 x [Samples in Buffer] | 2 x 2 x [Samples in Buffer] | 2 x 2 x [Samples in Buffer] | 2 x 2 x [Samples in Buffer] | |

4 | Channels | 4 x [Samples in Buffer] | 4 x 2 x [Samples in Buffer] | 4 x 2 x [Samples in Buffer] | 4 x 2 x [Samples in Buffer] | |

8 | Channels | 8 x [Samples in Buffer] | 8 x 2 x [Samples in Buffer] | 8 x 2 x [Samples in Buffer] | 8 x 2 x [Samples in Buffer] | |

Digital I/O (701x or 702x ) or pattern generator boards (72xx)

|

| Buffer length to be programmed in Bytes |

|

| ||

| 8 bit mode | 16 bit mode |

| 32 bit mode | 64 bit mode |

|

| [Samples in Buffer] | 2 x [Samples in Buffer] |

| 4 x [Samples in Buffer] | 8 x [Samples in Buffer] |

|

Digital I/O board 7005 only |

|

|

|

|

| |

|

|

| Buffer length to be programmed in Bytes |

| ||

|

|

|

| |||

| 1 bit mode | 2 bit mode |

| 4 bit mode | 8 bit mode | 16 bit mode |

1 Channel | 1/8 x [Samples in Buffer] | 1/4 x [Samples in Buffer] |

| 1/2 x [Samples in Buffer] | [Samples in Buffer] | 2 x [Samples in Buffer] |

We at Spectrum achieved best results when programming the buffer length to a number of samples that can hold approximately 100 ms of data. However if going to the limit of the PCI bus with the FIFO mode or when having buffer overruns it can be useful to have larger FIFO buffers to buffer more data in it.

When the goal is a fast update in FIFO mode smaller buffers and a larger number of buffers can be a better setup.

Register | Value | Direction | Description |

SPC_FIFO_BUFADR0 | 60100 | r/w | 32 bit address of FIFO buffer 0. Must be allocated by application program |

SPC_FIFO_BUFADR1 | 60101 | r/w | 32 bit address of FIFO buffer 1. Must be allocated by application program |

|

|

|

|

... |

|

| ... |

|

|

|

|

SPC_FIFO_BUFADR255 | 60355 | r/w | 32 bit address of FIFO buffer 255. Must be allocated by application program |

The driver handles the programmed number of buffers. To speed up FIFO transfer the driver uses buffers that are allocated and maintained by the application program. Before starting the FIFO mode the addresses of the allocated buffers must be set to the driver.

Example of FIFO buffer setup. No memory allocation error checking in the example to improve readability:

// | setup FIFO buffers | 64); | // 64 FIFO buffers used in the example | |

SpcSetParam | (hDrv, SPC_FIFO_BUFFERS, | |||

SpcSetParam | (hDrv, SPC_FIFO_BUFLEN, | 8192); | // Each FIFO buffer is 8 kBytes long | |

// | allocate memory for data |

|

| |

for (i = | 0; | i < 64; i++) |

| // memory allocation for 12, 14, 16 bit analog boards |

pnData[i] = (ptr16) malloc (8192); |

| |||

// pbyData[i] = (ptr8) malloc (8192); |

| // and digital boards | ||

| // memory allocation for 8 bit analog boards | |||

// | tell the used buffer adresses to the driver | |||

for (i = | 0; | i < 64; i++) |

|

|

nErr = SpcSetParam (hDrv, SPC_FIFO_BUFADR0 + i, | (int32) pnData[i]); // for 12, 14, 16 bit analog boards |

// nErr = SpcSetParam (hDrv, SPC_FIFO_BUFADR0 + i, | // and digital boards only |

(int32) pbyData[i]); // for 8 bit analog boards only |

Buffer processing

The driver counts all the software buffers that have been transferred. This number can be read out from the driver to know the exact amount of data that has been transferred.

Register | Value | Direction | Description |

SPC_FIFO_BUFCOUNT | 60020 | r | Number of transferred buffers until now |

If one knows before starting FIFO mode how long this should run it is possible to program the numer of buffers that the driver should process. After transferring this number of buffer the driver will automatically stop. If FIFO mode should run endless a zero must be programmed to this register. Then the FIFO mode must be stoped by the user.

Register | Value | Direction | Description |

SPC_FIFO_BUFMAXCNT | 60030 | r/w | Number of buffers to be transferred until automatic stop. Zero runs endless |

(c) Spectrum GmbH | 55 |