Synchronization (Option) | Setup synchronization for use with FIFO mode and equally clokked boards |

|

|

Additions for equal boards with different sample rates

In addition to the possibility of synchronizing different types of boards to one synchronous sample rate it can be also useful in some cases to synchronize boards of the same type, with one working at a divided speed.

In this case you simply set up the fastest board as the clock master and set it’s clock divider to one. Now you can easily generate divided clock rates on the slave boards by setting their dividers to according values of the divider list.

Please keep in mind that only the dedicated divider values mentioned in the list above can be used to derive the sample rates of the slave boards.

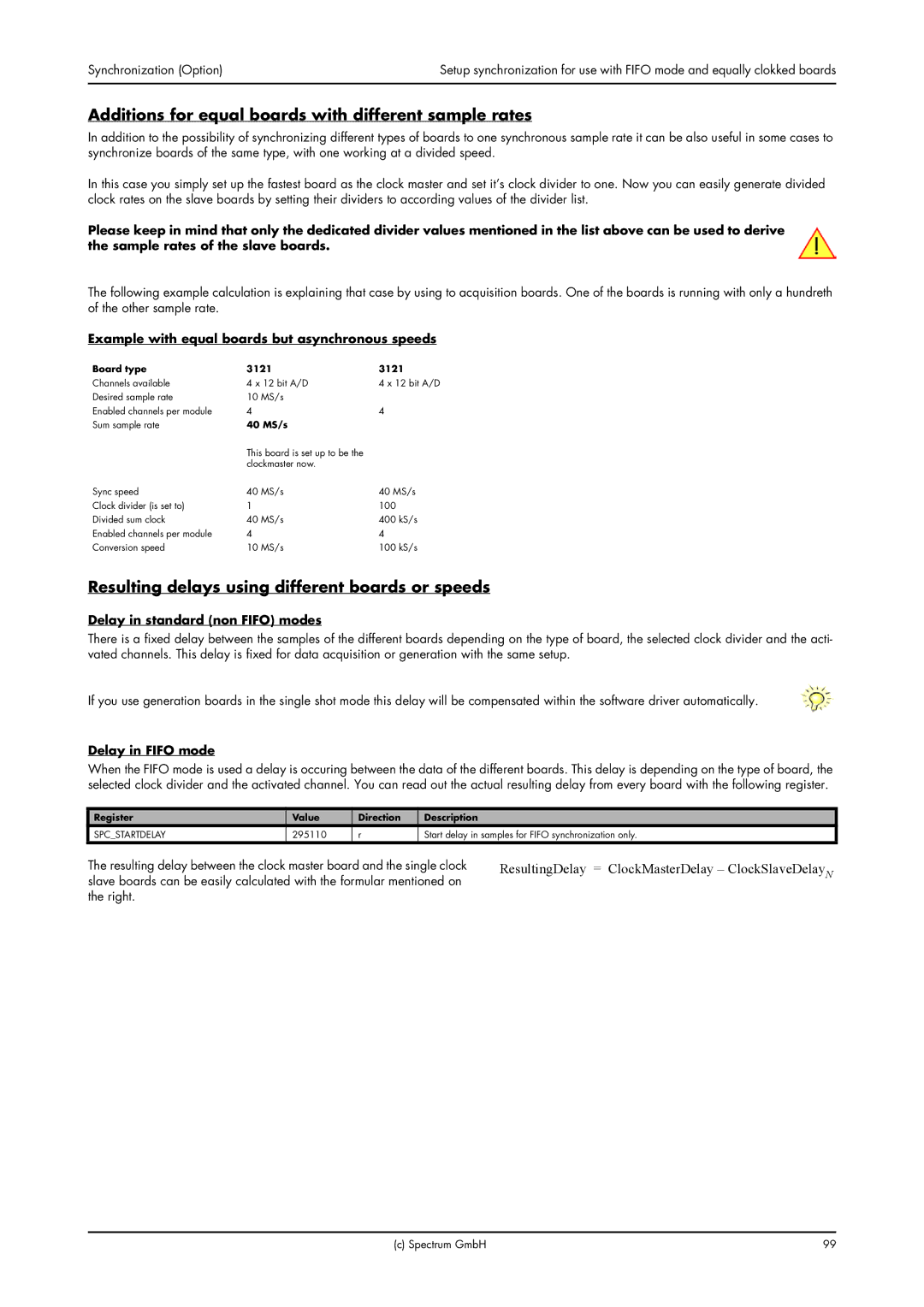

The following example calculation is explaining that case by using to acquisition boards. One of the boards is running with only a hundreth of the other sample rate.

Example with equal boards but asynchronous speeds

Board type | 3121 | 3121 |

Channels available | 4 x 12 bit A/D | 4 x 12 bit A/D |

Desired sample rate | 10 MS/s |

|

Enabled channels per module | 4 | 4 |

Sum sample rate | 40 MS/s |

|

| This board is set up to be the |

|

| clockmaster now. |

|

Sync speed | 40 MS/s | 40 MS/s |

Clock divider (is set to) | 1 | 100 |

Divided sum clock | 40 MS/s | 400 kS/s |

Enabled channels per module | 4 | 4 |

Conversion speed | 10 MS/s | 100 kS/s |

Resulting delays using different boards or speeds

Delay in standard (non FIFO) modes

There is a fixed delay between the samples of the different boards depending on the type of board, the selected clock divider and the acti- vated channels. This delay is fixed for data acquisition or generation with the same setup.

If you use generation boards in the single shot mode this delay will be compensated within the software driver automatically.

Delay in FIFO mode

When the FIFO mode is used a delay is occuring between the data of the different boards. This delay is depending on the type of board, the selected clock divider and the activated channel. You can read out the actual resulting delay from every board with the following register.

Register | Value | Direction | Description |

|

SPC_STARTDELAY | 295110 | r | Start delay in samples for FIFO synchronization only. | |

The resulting delay between the clock master board and the single clock | ResultingDelay = ClockMasterDelay – ClockSlaveDelayN | |||

slave boards can be easily calculated with the formular mentioned on |

| |||

the right.

(c) Spectrum GmbH | 99 |