Setup synchronization for use with FIFO mode and equally clokked boards | Synchronization (Option) |

|

|

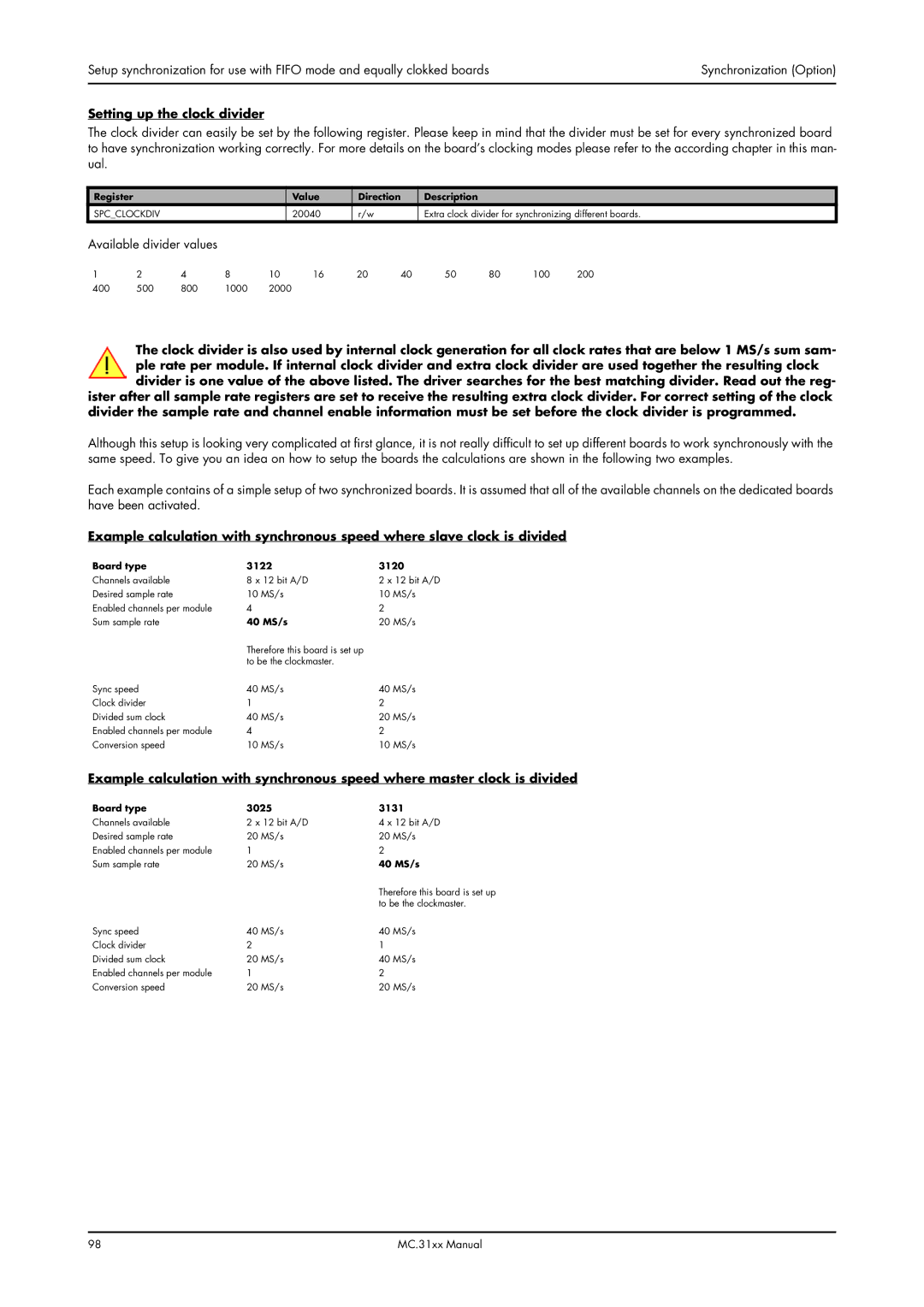

Setting up the clock divider

The clock divider can easily be set by the following register. Please keep in mind that the divider must be set for every synchronized board to have synchronization working correctly. For more details on the board’s clocking modes please refer to the according chapter in this man- ual.

Register | Value | Direction | Description |

SPC_CLOCKDIV | 20040 | r/w | Extra clock divider for synchronizing different boards. |

Available divider values

1 | 2 | 4 | 8 | 10 | 16 | 20 | 40 | 50 | 80 | 100 | 200 |

400 | 500 | 800 | 1000 | 2000 |

|

|

|

|

|

|

|

The clock divider is also used by internal clock generation for all clock rates that are below 1 MS/s sum sam- ple rate per module. If internal clock divider and extra clock divider are used together the resulting clock divider is one value of the above listed. The driver searches for the best matching divider. Read out the reg-

ister after all sample rate registers are set to receive the resulting extra clock divider. For correct setting of the clock divider the sample rate and channel enable information must be set before the clock divider is programmed.

Although this setup is looking very complicated at first glance, it is not really difficult to set up different boards to work synchronously with the same speed. To give you an idea on how to setup the boards the calculations are shown in the following two examples.

Each example contains of a simple setup of two synchronized boards. It is assumed that all of the available channels on the dedicated boards have been activated.

Example calculation with synchronous speed where slave clock is divided

Board type | 3122 | 3120 |

Channels available | 8 x 12 bit A/D | 2 x 12 bit A/D |

Desired sample rate | 10 MS/s | 10 MS/s |

Enabled channels per module | 4 | 2 |

Sum sample rate | 40 MS/s | 20 MS/s |

| Therefore this board is set up |

|

| to be the clockmaster. |

|

Sync speed | 40 MS/s | 40 MS/s |

Clock divider | 1 | 2 |

Divided sum clock | 40 MS/s | 20 MS/s |

Enabled channels per module | 4 | 2 |

Conversion speed | 10 MS/s | 10 MS/s |

Example calculation with synchronous speed where master clock is divided

Board type | 3025 | 3131 |

Channels available | 2 x 12 bit A/D | 4 x 12 bit A/D |

Desired sample rate | 20 MS/s | 20 MS/s |

Enabled channels per module | 1 | 2 |

Sum sample rate | 20 MS/s | 40 MS/s |

|

| Therefore this board is set up |

|

| to be the clockmaster. |

Sync speed | 40 MS/s | 40 MS/s |

Clock divider | 2 | 1 |

Divided sum clock | 20 MS/s | 40 MS/s |

Enabled channels per module | 1 | 2 |

Conversion speed | 20 MS/s | 20 MS/s |

98 | MC.31xx Manual |