Chapter 3 |

|

|

|

|

|

|

|

|

|

| Signals and Pinout Tables | ||||||||

Table |

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

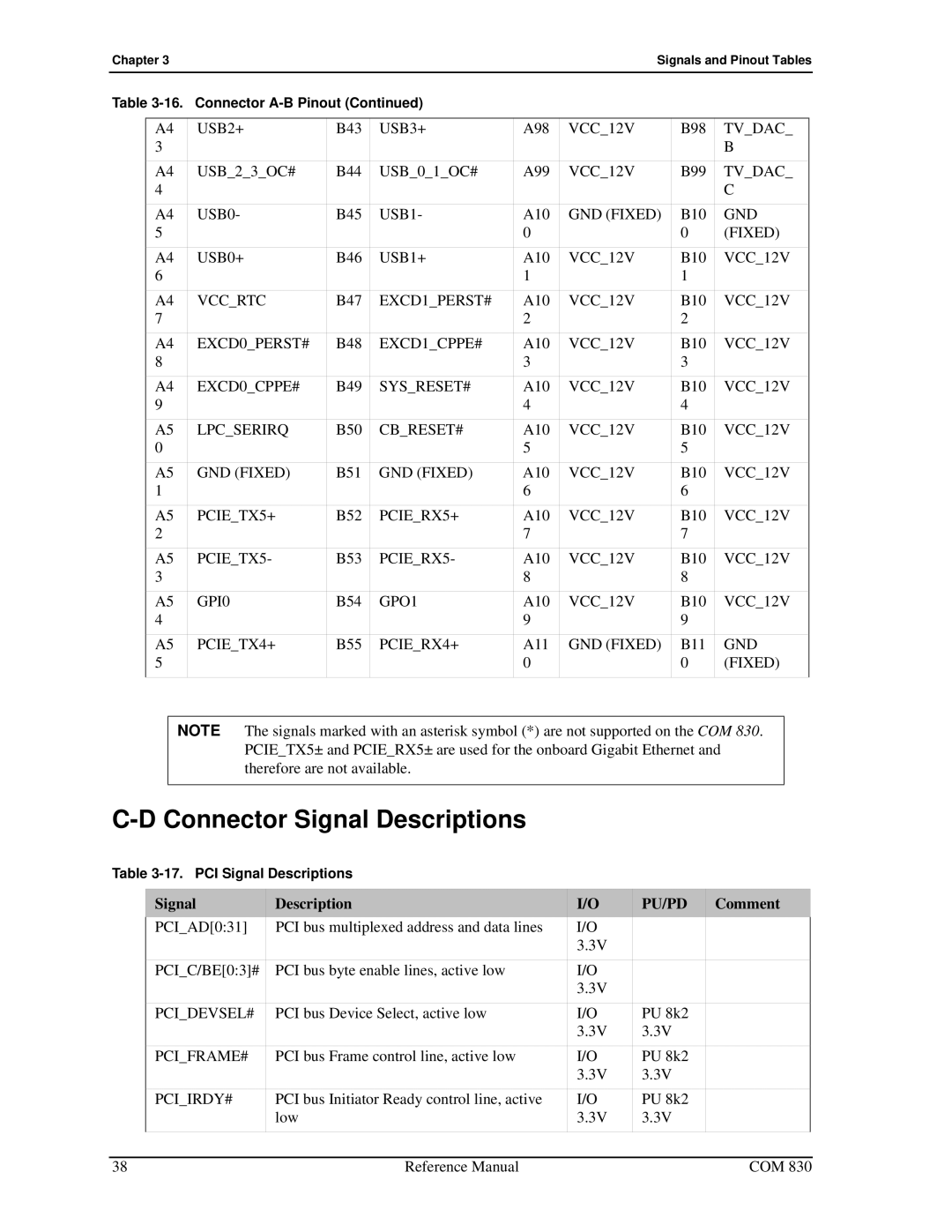

| A4 |

| USB2+ |

| B43 | USB3+ |

| A98 |

| VCC_12V |

|

| B98 | TV_DAC_ | |||||

| 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| B | |

| A4 |

| USB_2_3_OC# | B44 | USB_0_1_OC# |

| A99 |

| VCC_12V |

|

| B99 | TV_DAC_ | ||||||

| 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C | |

| A4 |

| USB0- |

| B45 | USB1- |

| A10 |

| GND (FIXED) |

| B10 | GND | ||||||

| 5 |

|

|

|

|

|

|

|

| 0 |

|

|

|

|

| 0 |

| (FIXED) | |

| A4 |

| USB0+ |

| B46 | USB1+ |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | |||||

| 6 |

|

|

|

|

|

|

|

| 1 |

|

|

|

|

| 1 |

|

|

|

| A4 |

| VCC_RTC |

| B47 | EXCD1_PERST# |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | |||||

| 7 |

|

|

|

|

|

|

|

| 2 |

|

|

|

|

| 2 |

|

|

|

| A4 |

| EXCD0_PERST# | B48 | EXCD1_CPPE# |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | ||||||

| 8 |

|

|

|

|

|

|

|

| 3 |

|

|

|

|

| 3 |

|

|

|

| A4 |

| EXCD0_CPPE# | B49 | SYS_RESET# |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | ||||||

| 9 |

|

|

|

|

|

|

|

| 4 |

|

|

|

|

| 4 |

|

|

|

| A5 |

| LPC_SERIRQ | B50 | CB_RESET# |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | ||||||

| 0 |

|

|

|

|

|

|

|

| 5 |

|

|

|

|

| 5 |

|

|

|

| A5 |

| GND (FIXED) | B51 | GND (FIXED) |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | ||||||

| 1 |

|

|

|

|

|

|

|

| 6 |

|

|

|

|

| 6 |

|

|

|

| A5 |

| PCIE_TX5+ | B52 | PCIE_RX5+ |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | ||||||

| 2 |

|

|

|

|

|

|

|

| 7 |

|

|

|

|

| 7 |

|

|

|

| A5 |

| PCIE_TX5- |

| B53 | PCIE_RX5- |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | |||||

| 3 |

|

|

|

|

|

|

|

| 8 |

|

|

|

|

| 8 |

|

|

|

| A5 |

| GPI0 |

| B54 | GPO1 |

| A10 |

| VCC_12V |

|

| B10 | VCC_12V | |||||

| 4 |

|

|

|

|

|

|

|

| 9 |

|

|

|

|

| 9 |

|

|

|

| A5 |

| PCIE_TX4+ | B55 | PCIE_RX4+ |

| A11 |

| GND (FIXED) |

| B11 | GND | |||||||

| 5 |

|

|

|

|

|

|

|

| 0 |

|

|

|

|

| 0 |

| (FIXED) | |

|

|

|

|

|

|

|

| ||||||||||||

|

| NOTE The signals marked with an asterisk symbol (*) are not supported on the COM 830. |

| ||||||||||||||||

|

|

|

| PCIE_TX5± and PCIE_RX5± are used for the onboard Gigabit Ethernet and |

| ||||||||||||||

|

|

|

| therefore are not available. |

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

| |||||||||||

Table |

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| Signal |

|

| Description |

|

|

|

| I/O |

| PU/PD |

| Comment | ||||||

| PCI_AD[0:31] | PCI bus multiplexed address and data lines | I/O |

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

| 3.3V |

|

|

|

|

|

|

|

| PCI_C/BE[0:3]# |

| PCI bus byte enable lines, active low |

|

| I/O |

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| 3.3V |

|

|

|

|

|

|

|

| PCI_DEVSEL# |

| PCI bus Device Select, active low |

|

| I/O |

| PU 8k2 |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| 3.3V |

| 3.3V |

|

|

|

| |

| PCI_FRAME# |

| PCI bus Frame control line, active low |

|

| I/O |

| PU 8k2 |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| 3.3V |

| 3.3V |

|

|

|

| |

| PCI_IRDY# |

| PCI bus Initiator Ready control line, active | I/O |

| PU 8k2 |

|

|

| ||||||||||

|

|

|

|

|

| low |

|

|

|

|

| 3.3V |

| 3.3V |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 | Reference Manual | COM 830 |