Chapter 3Signals and Pinout Tables

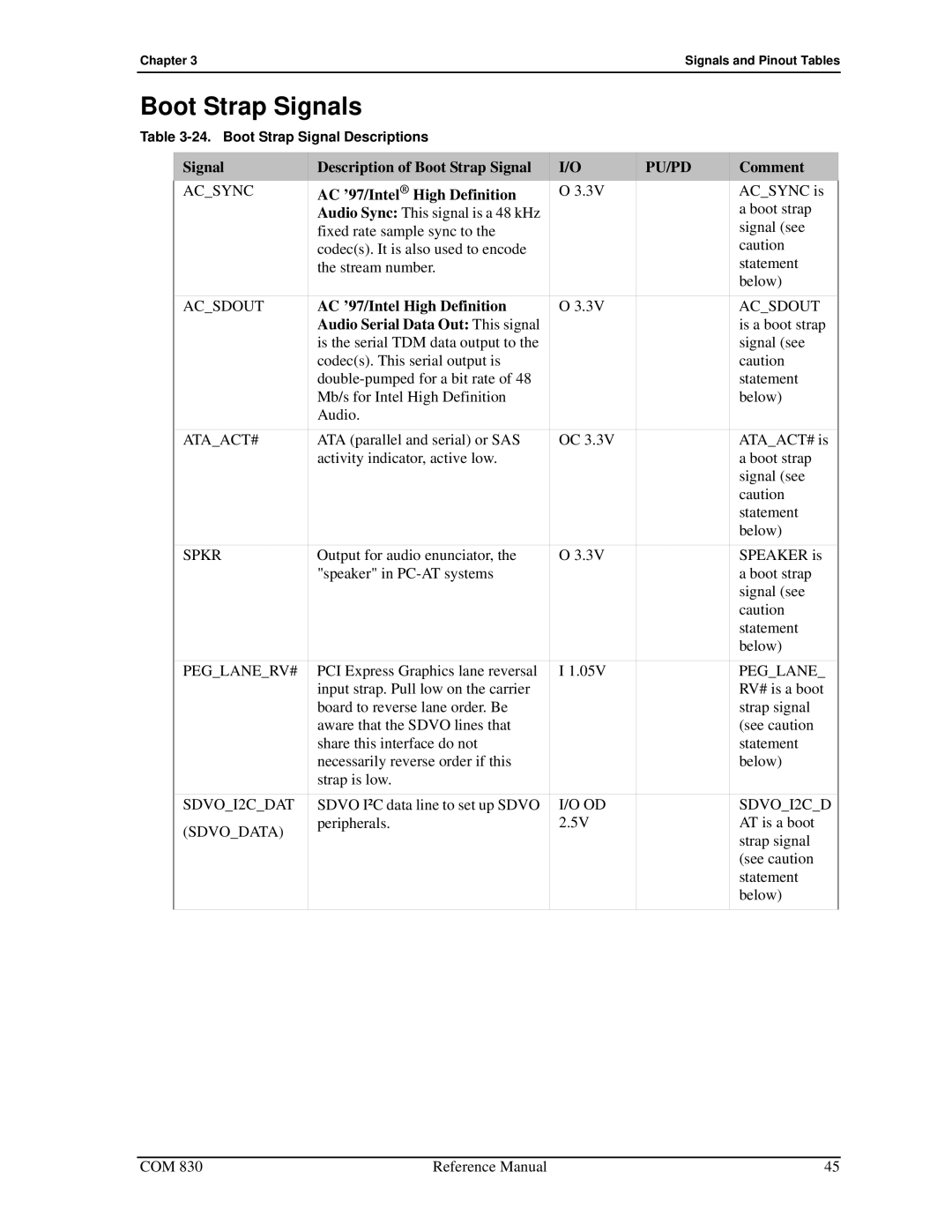

Boot Strap Signals

Table

Signal | Description of Boot Strap Signal | I/O | PU/PD | Comment |

AC_SYNC | AC ’97/Intel® High Definition | O 3.3V |

| AC_SYNC is |

| Audio Sync: This signal is a 48 kHz |

|

| a boot strap |

| fixed rate sample sync to the |

|

| signal (see |

| codec(s). It is also used to encode |

|

| caution |

| the stream number. |

|

| statement |

|

|

|

| below) |

AC_SDOUT | AC ’97/Intel High Definition | O 3.3V |

| AC_SDOUT |

| Audio Serial Data Out: This signal |

|

| is a boot strap |

| is the serial TDM data output to the |

|

| signal (see |

| codec(s). This serial output is |

|

| caution |

|

|

| statement | |

| Mb/s for Intel High Definition |

|

| below) |

| Audio. |

|

|

|

ATA_ACT# | ATA (parallel and serial) or SAS | OC 3.3V |

| ATA_ACT# is |

| activity indicator, active low. |

|

| a boot strap |

|

|

|

| signal (see |

|

|

|

| caution |

|

|

|

| statement |

|

|

|

| below) |

SPKR | Output for audio enunciator, the | O 3.3V |

| SPEAKER is |

| "speaker" in |

|

| a boot strap |

|

|

|

| signal (see |

|

|

|

| caution |

|

|

|

| statement |

|

|

|

| below) |

PEG_LANE_RV# | PCI Express Graphics lane reversal | I 1.05V |

| PEG_LANE_ |

| input strap. Pull low on the carrier |

|

| RV# is a boot |

| board to reverse lane order. Be |

|

| strap signal |

| aware that the SDVO lines that |

|

| (see caution |

| share this interface do not |

|

| statement |

| necessarily reverse order if this |

|

| below) |

| strap is low. |

|

|

|

SDVO_I2C_DAT | SDVO I²C data line to set up SDVO | I/O OD |

| SDVO_I2C_D |

(SDVO_DATA) | peripherals. | 2.5V |

| AT is a boot |

|

|

| strap signal | |

|

|

|

| |

|

|

|

| (see caution |

|

|

|

| statement |

|

|

|

| below) |

|

|

|

|

|

COM 830 | Reference Manual | 45 |