J4 IDC

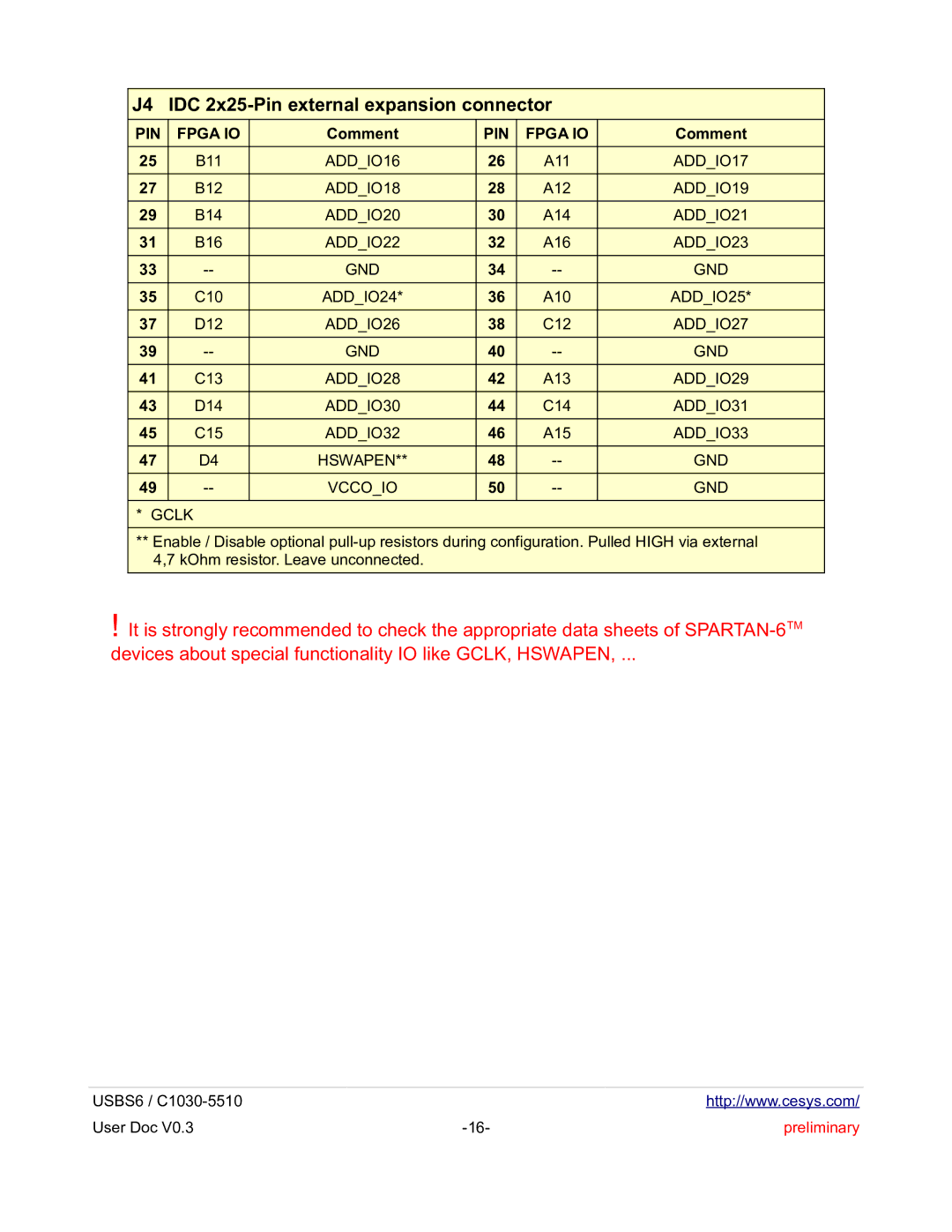

J4 IDC 2x25-Pin external expansion connector

PIN | FPGA IO | Comment | PIN | FPGA IO | Comment |

25 | B11 | ADD_IO16 | 26 | A11 | ADD_IO17 |

27 | B12 | ADD_IO18 | 28 | A12 | ADD_IO19 |

29 | B14 | ADD_IO20 | 30 | A14 | ADD_IO21 |

31 | B16 | ADD_IO22 | 32 | A16 | ADD_IO23 |

33 | GND | 34 | GND | ||

35 | C10 | ADD_IO24* | 36 | A10 | ADD_IO25* |

37 | D12 | ADD_IO26 | 38 | C12 | ADD_IO27 |

|

|

|

|

|

|

39 | GND | 40 | GND | ||

41 | C13 | ADD_IO28 | 42 | A13 | ADD_IO29 |

43 | D14 | ADD_IO30 | 44 | C14 | ADD_IO31 |

|

|

|

|

|

|

45 | C15 | ADD_IO32 | 46 | A15 | ADD_IO33 |

47 | D4 | HSWAPEN** | 48 | GND | |

49 | VCCO_IO | 50 | GND |

![]() * GCLK

* GCLK

**Enable / Disable optional

!It is strongly recommended to check the appropriate data sheets of

USBS6 / |

| http://www.cesys.com/ |

User Doc V0.3 | preliminary |