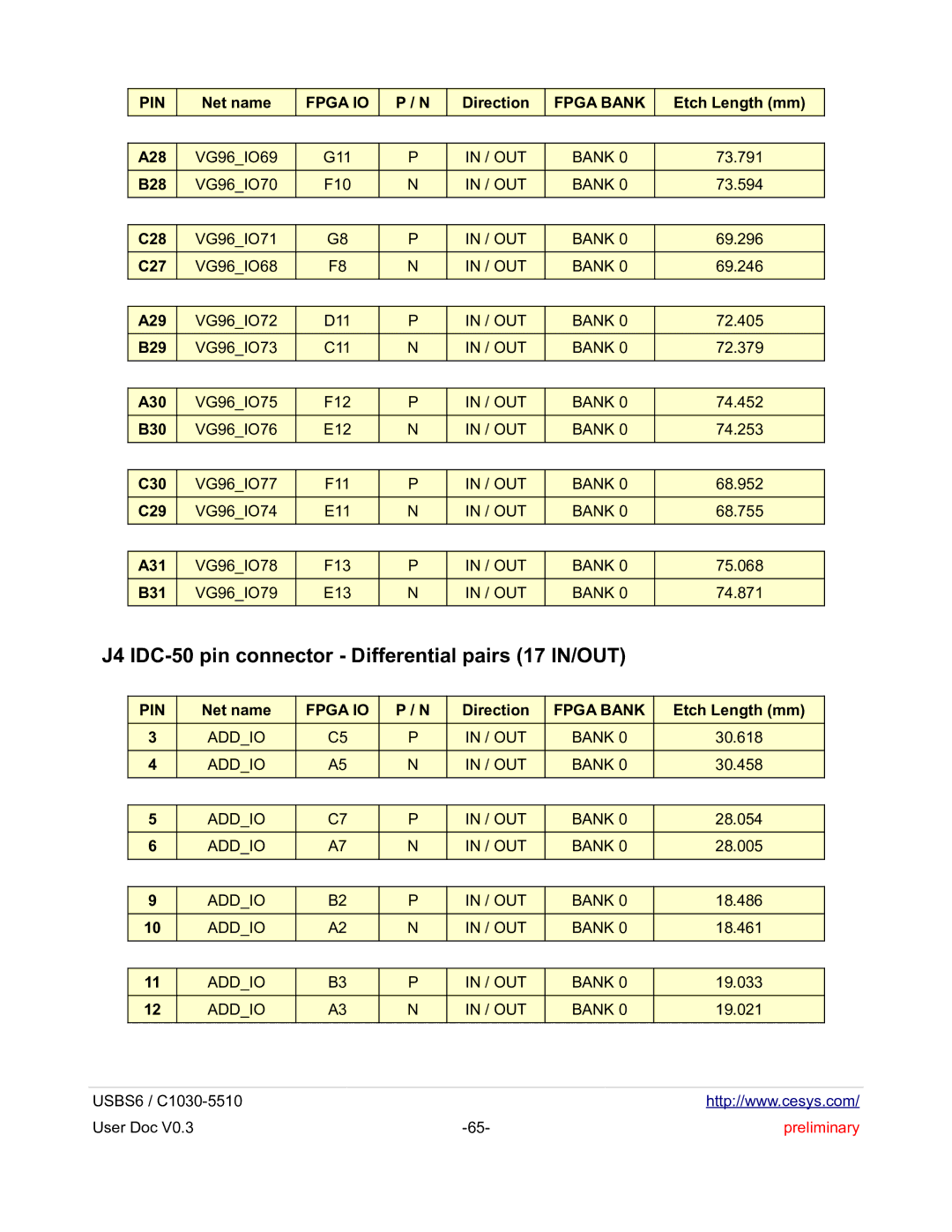

PIN

Net name

FPGA IO

P / N

Direction  FPGA BANK

FPGA BANK  Etch Length (mm)

Etch Length (mm)

A28 | VG96_IO69 | G11 | P | IN / OUT | BANK 0 | 73.791 |

B28 | VG96_IO70 | F10 | N | IN / OUT | BANK 0 | 73.594 |

|

|

|

|

|

|

|

C28 | VG96_IO71 | G8 | P | IN / OUT | BANK 0 | 69.296 |

C27 | VG96_IO68 | F8 | N | IN / OUT | BANK 0 | 69.246 |

|

|

|

|

|

|

|

A29 | VG96_IO72 | D11 | P | IN / OUT | BANK 0 | 72.405 |

B29 | VG96_IO73 | C11 | N | IN / OUT | BANK 0 | 72.379 |

|

|

|

|

|

|

|

A30 | VG96_IO75 | F12 | P | IN / OUT | BANK 0 | 74.452 |

B30 | VG96_IO76 | E12 | N | IN / OUT | BANK 0 | 74.253 |

|

|

|

|

|

|

|

C30 | VG96_IO77 | F11 | P | IN / OUT | BANK 0 | 68.952 |

C29 | VG96_IO74 | E11 | N | IN / OUT | BANK 0 | 68.755 |

|

|

|

|

|

|

|

A31 | VG96_IO78 | F13 | P | IN / OUT | BANK 0 | 75.068 |

B31 | VG96_IO79 | E13 | N | IN / OUT | BANK 0 | 74.871 |

|

|

|

|

|

|

|

J4 IDC-50 pin connector - Differential pairs (17 IN/OUT)

PIN | Net name | FPGA IO | P / N | Direction | FPGA BANK | Etch Length (mm) |

3 | ADD_IO | C5 | P | IN / OUT | BANK 0 | 30.618 |

4 | ADD_IO | A5 | N | IN / OUT | BANK 0 | 30.458 |

|

|

|

|

|

|

|

5 | ADD_IO | C7 | P | IN / OUT | BANK 0 | 28.054 |

6 | ADD_IO | A7 | N | IN / OUT | BANK 0 | 28.005 |

|

|

|

|

|

|

|

9 | ADD_IO | B2 | P | IN / OUT | BANK 0 | 18.486 |

10 | ADD_IO | A2 | N | IN / OUT | BANK 0 | 18.461 |

|

|

|

|

|

|

|

11 | ADD_IO | B3 | P | IN / OUT | BANK 0 | 19.033 |

12 | ADD_IO | A3 | N | IN / OUT | BANK 0 | 19.021 |

USBS6 / |

| http://www.cesys.com/ |

User Doc V0.3 | preliminary |