VHDL. Verilog and schematic entry design flows are not supported.

•The design “usbs6_soc” demonstrates the implementation of a system-on-chip (SoC) with host software access to the peripherals like GPIOs, external Flash Memory, LPDDR Memory and internal BlockRAM over USB. This design requires a protocol layer over the simple USB bulk transfer (see CESYS application note “Transfer Protocol for CESYS USB products” for details), which is already provided by CESYS software API.

•The design “usbs6_bram” is a minimal example for data transfers from and to the FPGA over USB and can be used to get for familiar with UDK hardware/software interface.

The Spartan-6 XC6SLX16 Device is supported by the free XilinxTM ISE Webpack development software. You will have to change some options of the project properties for own applications.

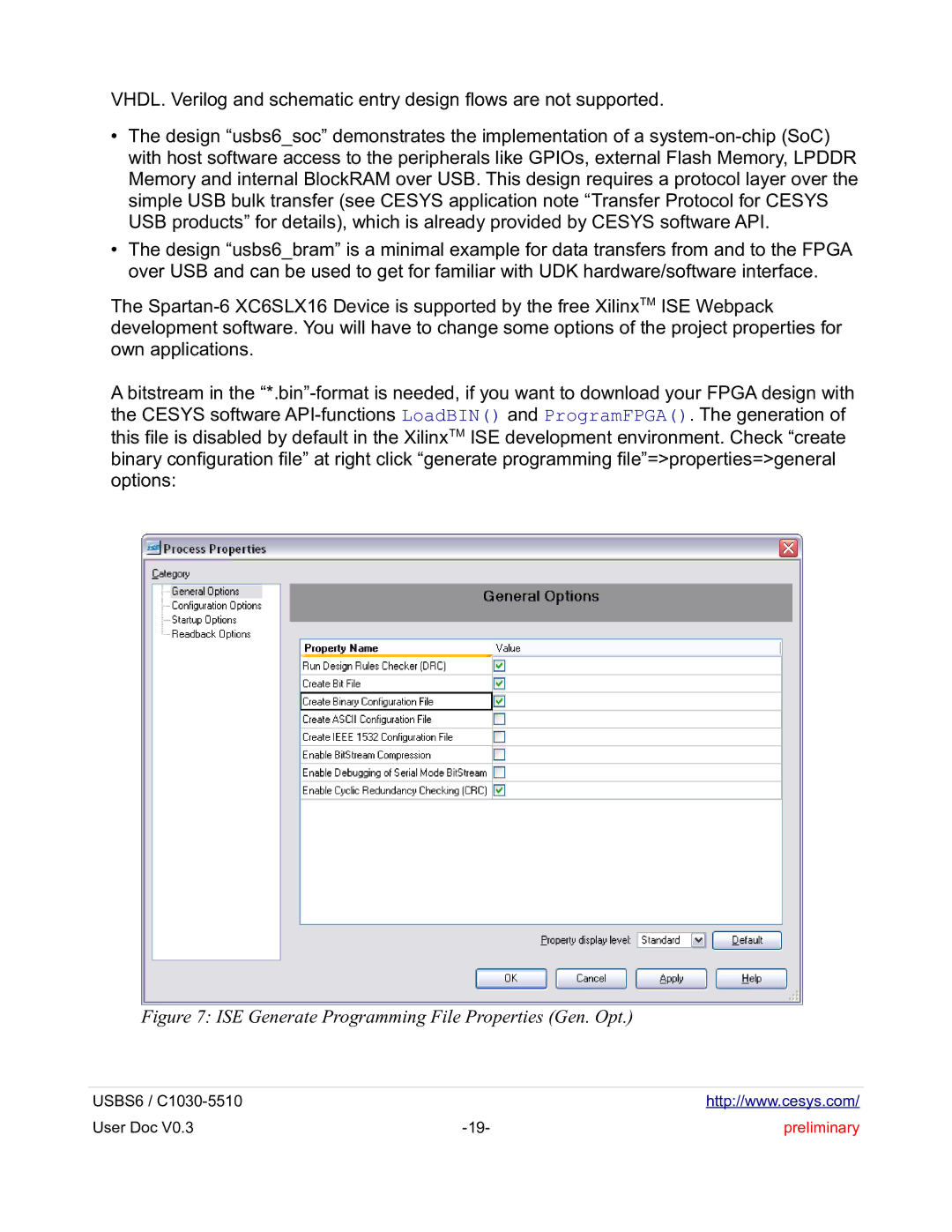

A bitstream in the “*.bin”-format is needed, if you want to download your FPGA design with the CESYS software API-functions LoadBIN() and ProgramFPGA(). The generation of this file is disabled by default in the XilinxTM ISE development environment. Check “create binary configuration file” at right click “generate programming file”=>properties=>general options:

Figure 7: ISE Generate Programming File Properties (Gen. Opt.)

USBS6 / C1030-5510 | | http://www.cesys.com/ |

User Doc V0.3 | -19- | preliminary |