•Download design from host

•Load design from flash (supported on EFM01, USBV4F and USBS6)

So the first entry in the initialize list must be a program entry or, if loaded from flash, a reset entry (To sync communication to the host side). Subsequent to this, a mix of register write and sleep commands can be placed, which totally depends on the underlying FPGA design. This can be a sequence of commands sent to a peripheral component or to fill data structures with predefined values. If things get complexer, i.e. return values must be checked, this goes beyond the scope of the current UDKLab implementation and must be solved by a host process.

To control the sequence, the buttons on the left side can be used. In the order of appearance, they do the following (also indicated by tooltips):

•Clear complete list

•Add new entry (to the end of the list)

•Move currently selected entry on position up

•Move currently selected entry on position down

•Remove currently selected entry

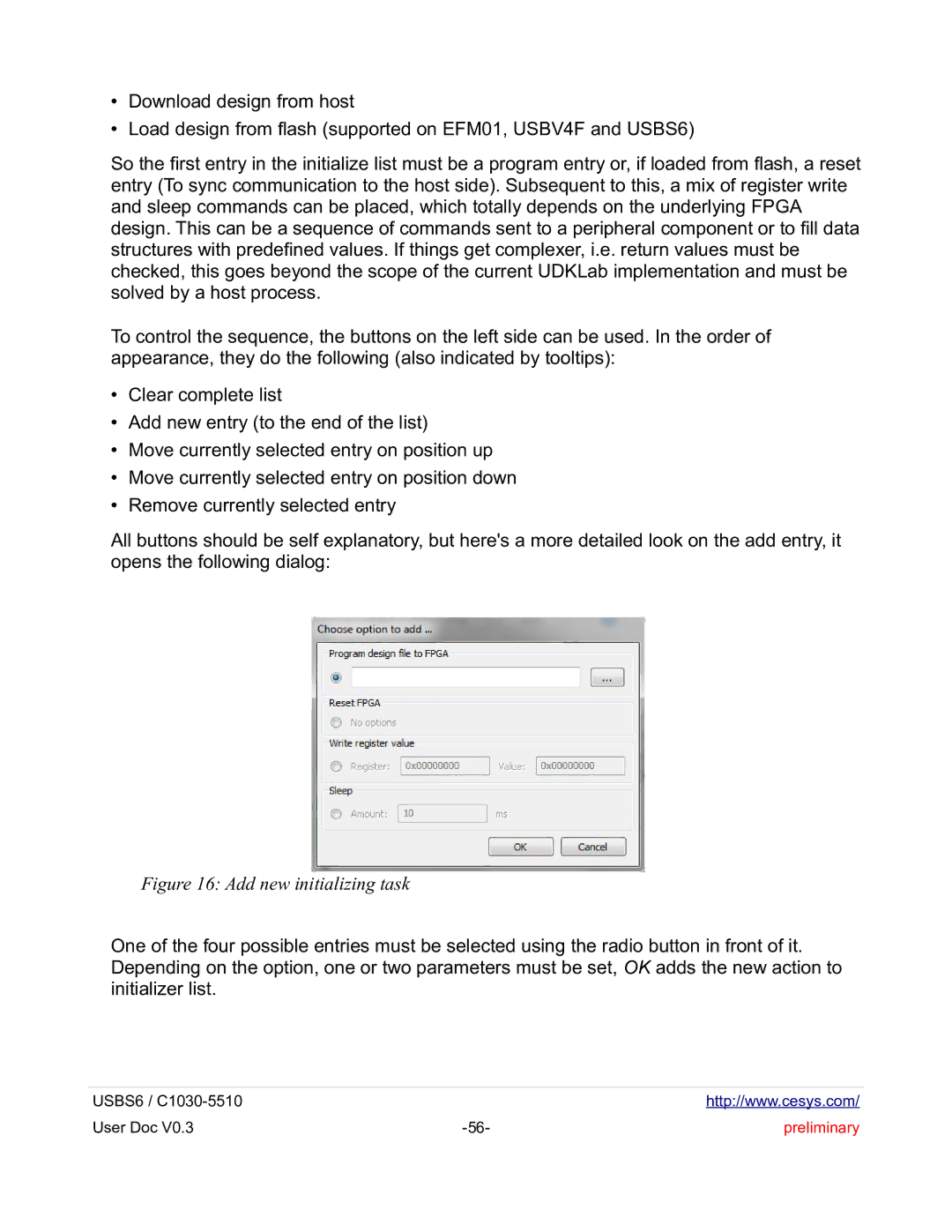

All buttons should be self explanatory, but here's a more detailed look on the add entry, it opens the following dialog:

Figure 16: Add new initializing task

One of the four possible entries must be selected using the radio button in front of it. Depending on the option, one or two parameters must be set, OK adds the new action to initializer list.

USBS6 / |

| http://www.cesys.com/ |

User Doc V0.3 | preliminary |