ifclk |

|

|

|

|

|

|

app_fifo_wr_i |

|

|

|

|

|

|

app_fifo_wr_data_i | D0 | D1 | D2 | D3 | D4 |

|

app_fifo_wr_full_o |

|

|

|

|

|

|

app_fifo_wr_count_o | 122 | 123 | 124 | 125 | 126 | 127 |

![]() FPGA =>

FPGA =>

ifclk |

|

|

|

|

|

|

app_fifo_rd_i |

|

|

|

|

|

|

app_fifo_rd_data_o |

| D4 | D3 | D2 | D1 | D0 |

app_fifo_rd_empty_o |

|

|

|

|

|

|

app_fifo_rd_count_o | 5 | 4 | 3 | 2 | 1 | 0 |

Figure 9: FIFO transactions of fx2_slfifo_ctrl at user logic side

![]()

![]()

![]() FX-2

FX-2

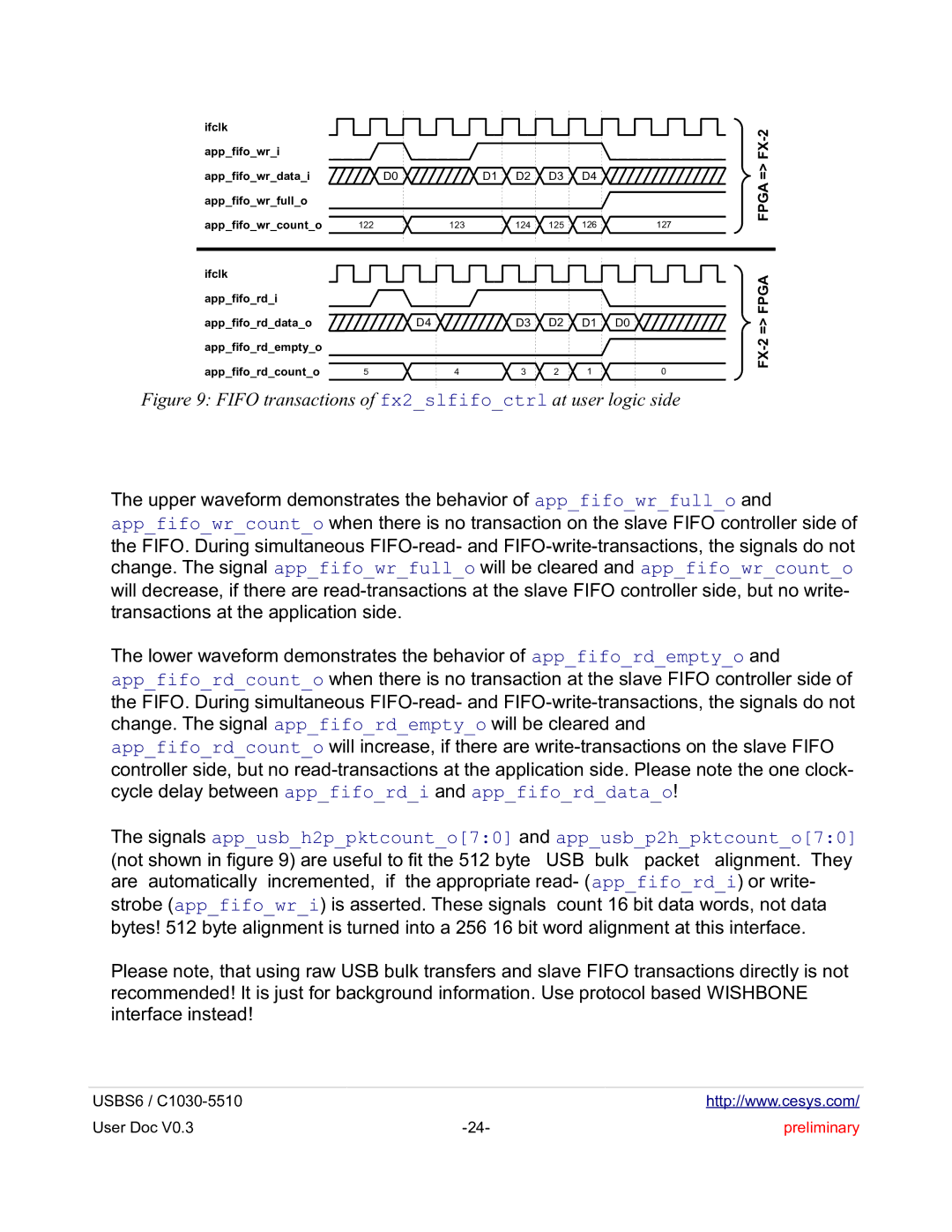

The upper waveform demonstrates the behavior of app_fifo_wr_full_o and

app_fifo_wr_count_o when there is no transaction on the slave FIFO controller side of the FIFO. During simultaneous

The lower waveform demonstrates the behavior of app_fifo_rd_empty_o and

app_fifo_rd_count_o when there is no transaction at the slave FIFO controller side of the FIFO. During simultaneous

The signals app_usb_h2p_pktcount_o[7:0] and app_usb_p2h_pktcount_o[7:0]

(not shown in figure 9) are useful to fit the 512 byte USB bulk packet alignment. They are automatically incremented, if the appropriate read- (app_fifo_rd_i) or write- strobe (app_fifo_wr_i) is asserted. These signals count 16 bit data words, not data bytes! 512 byte alignment is turned into a 256 16 bit word alignment at this interface.

Please note, that using raw USB bulk transfers and slave FIFO transactions directly is not recommended! It is just for background information. Use protocol based WISHBONE interface instead!

USBS6 / |

| http://www.cesys.com/ |

User Doc V0.3 | preliminary |