Muitimeter

Tt,,,,t

Hewlewpackard

ManualPartNo MicrofichePartNo

PrintedAPRIL

Tableofcontents

C0NTENTSGontd

RABLEOFCONTENTSCont,d

Listofillustbations

PorariryR,tüä

Diagram Äl,il ?7l+eatic ?rorr

ACAdiGüffi

Frz

0PT0NS

12ACCESSORIES.AVAITABLE

1lNTBoDucTl0N

SPECTFtCATI0NS

14INSTBUMENT.AND Manualidentifica T I O N

35+o . os +o . o2s

Lo . t

8 1 5 0

Contd Specifications

Oo7 .005 .0m

O07 .oo5

1000.0v

SpecificationsCont,d

00fiv

24hours23o 10c

Vin = vs/H rl

DVs/u

SectionI Model34904 GenerallnformationContd

Dvs/H

REc

NTR0DtCTloN

BenchUse

Installation

INSTALLATION.OFOPTIONS

LsolatedData0utput0ption021-hp-111ZlAl

Data0utput0ption021

Option050andOption060

29INTERFACE.CONNECTIONS

RemoteGontrol0ption022

SectionII Model34904 7N i 3i -s t** JrJü,1t

Fc ö

OPTtoN021

2H* F EI = 6 s i ä 2 qd E ? 3 5 fr i F 3 ä

REMOTEINPUTCONNECTORJ7

5 E E i F = =

= ! 9 i l

Cablepart NO. Length

RearInput

GeneralPurposelnterfaceBusConnections

10631A 6 3 1 10631C

9 9 f

GeneralPurposeInterfaceBusConnectors

GPIBBUSCONNECTORJl2

Outguard

TriggerConnections,GPIB0ption030

Sample/HoldConnections,0ption040/045

Repackagingforshipment

S7-30360-37s

D e l 3 4 9 0 a For J7 is -hp- Part No -0084 Amphenol

SectionIII Model3490A

13FRONT.ANDREARPANELOESCRIPTION

WARililG

Instbumentcapabilities

15MAXIMUM.INPUTVOLTAGES

Guarding

I7 . Generaloperatinginstructions

Turn-OnandWarm-Up

FloatingMeasurements

SELF.TESTOPERATION

Acvoltagemeasurements

Resistancemeasurements

InputConnections

60.0hmsSignalVoltageandCurrent

OutputSignalsandLevels

62.0hmmeterSampteRateandBesponseTime

79.0utputSignals

InputSignalRequirements

InputSignalsandLevels

Data0utputlsolation

SRo

GPIBBusSignals

030

DAC

RÄi+ -cg- lL

101Talk.0nlyNoController

103GPIB.Controlof3490A

L l

AddressCodes

To7

Asciicodecharacter Binarycode Octal Code

2 3 4 5 6

ProgramCodes

A R a C T E R

USE

Ldav

F D

Will acceptdata

Printerand 3490A

349OAand

Printerwill

Ooü 0 f R \ r @üoü@f E \

I X E D N I 1 J

GPIB0peratingExamPle

SetsLREN LOWon bus

To haltprogram,press

136Controlby.MarkedCardProgrammer

\tD?u6,.. TlE,, . ?5V

SroP l CMD?U6 OUTPUT13,30 ..M3R7F@E

27 l

349OA PRoonnvr LrrruE,ir

Or o o l 4 0 z o

F r

152Special.S/H0peratingGonsiderations

158Input.SignalLimitations

160Sample/Hold.TriggerSignalRequirements

156Guard.ConnectioninSample/HoldMeaurements

OtherOptions

165Initiating.Sample/HoldMeasurement

O40 O20

040 030

200

173Using.theTrack/HoldMode

Typicaltimereouiredto SETTLETO1 %

1000v

Voltageactually

Tnputvoltageat

M EO F S / HT R I G G E R

Measured

T a Vc-vs

179Using.theAcquire/HoldMode

V e

T s

$184.RATIOlfleasurements0ption080

182Using.50Hz or 60Hz PowerSourceOptions 050or060

RatioMeasrementProcedure

$186.ExternalBeferenceVoltages

Model3490A

4I . Intboduction

ßüy

+3 . Generaltheoryofoperation

+19 .DCANAL0GCIRCUITS

Display

RangeandFunctionControl

LnputAttenuator

+23. DCAmPlifier

SwitchingCircuits

BoottrapCircuit

+25. OCAmplifierGain

SectionIV Model3490A

Otui

Ls, ys

Rt-- c-++

Dual-SlopeIntegration

Integratorcircuits

IntegratingAmplifier

52AC.CONVEBTEB

L44. x 20Amplifier

ZercDetectAmplifier

ACAttenuators

Ohmsconverter

HmmeterPowerSupply

CurrentSource

InputProtection

+70 ISPLAYASSEMBLYFigure

HmmeterReference

DisplayUnits

TimingCounter

DataGounter

Buffers

M I N G

10. Block Diagram,Main LogicASM Flow Chart

R0,0m

11. Block Diagram,Main LogicCircuits

Model3490A Tl-90.AlgorithmicStateMachine

105Input.PolarityStorage

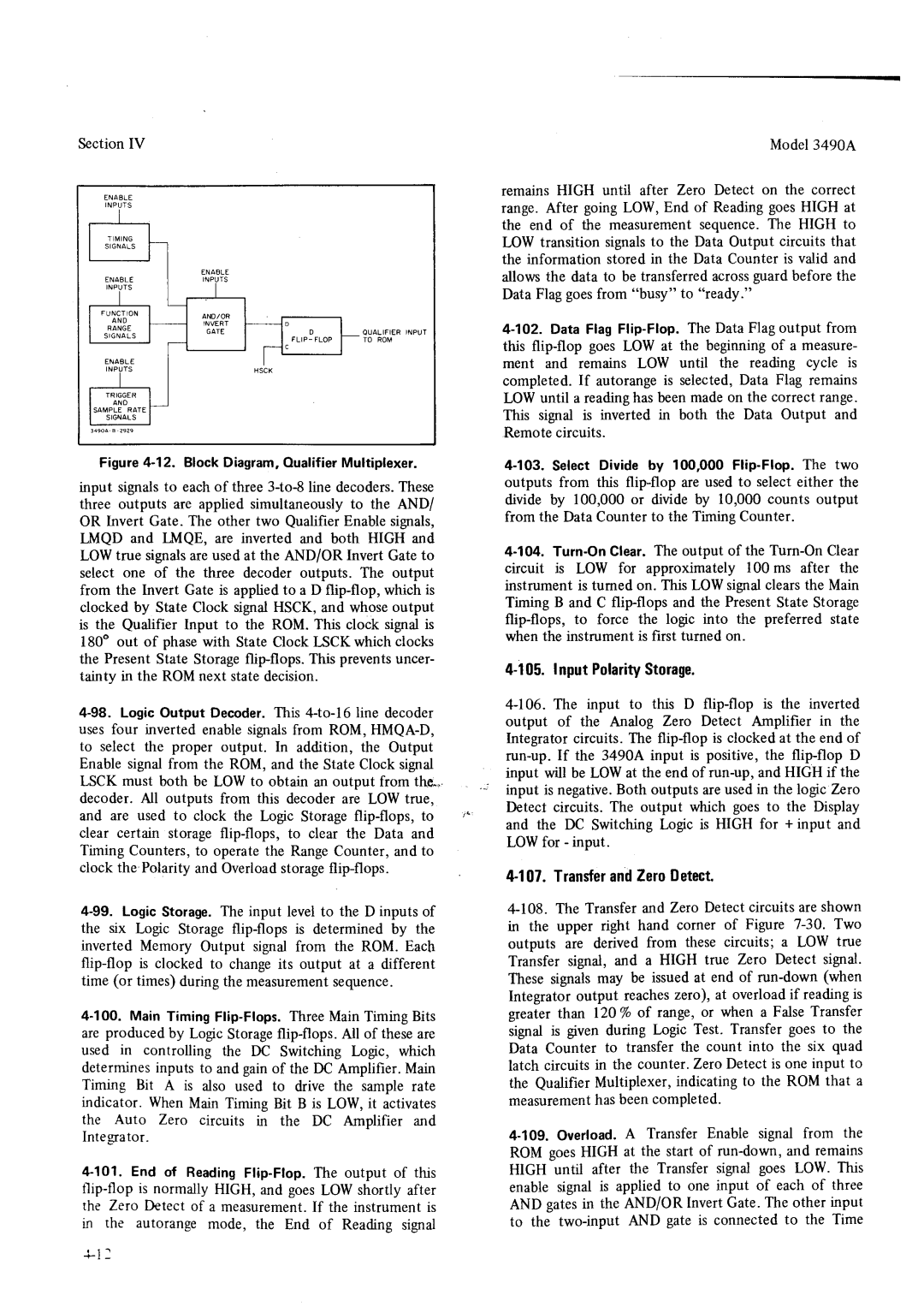

Enaele P U T S Enable Oualifierinput To ROM

TransferandZeroDetect

+il5. DCSWTTCHNGLoGrC

+II7 . Referencesupplies

RatioMeasrements0ption080

+ I 7

+128 .FBONTPANELS1VITCHING

Powersupplies

+ t

Polarityin Ratio Measurements

+I32 . Self . Testfunction

134Logic.Test,No.l

G H

+143.0.1VRangeZero,TestNo.b

TurnoverError,TestNo.3

+137.10V RangeZero,TestNo.2

4145.x .01Atten.x, 100Gain,TestNo.6

+158 .DATAOUTPUTOPTION021

4t74.REM0TEC0NTR0t0PTtoN022

+r9

DauFlag

+188.ShiftRegisters

LocaURemoteFlip-Flop

198GPIB.System

+2r

GPIBSystemOperation

+212.SAMPLE/H0tD0PTl0Nll40or045

Figwe 4-23. WaveformslllustratingAcquire/Hold Mode

216Acquire/Hold.Mode

+23

Too

Sample/HoldAnalogCircuits

@ n z

Compensation

Ja+z

Roo

TooK

+25

Flgure4-27. Sample/HoldLogic Block Diagram

228Sample/Hold.LogicCircuits

Lye e outpur

External

DC Amp

512 615.0 1000v 124.4 154.O

Exterml Hold H Hehs

Page

Figurb4-30. Sample/HoldMeasurementSequence

Ortoroo OruY --Jl

Example of TRACK/HOLD MEA Surementseouence

Waveformsarenot drawnto timeo, o,,rnI?lt

Integrator

I-r Gort +prr2zrs.i Qrs Sre Ero-+ 3r4 Zra Orr

RIOLD A1 bHOLD B r l l

RecommendedTestEquipment

10kn

Performancechecks S7. Performancetests

TNTB0DUCTIoN

Recommendedtesteouipment

$9. Dcvoltmeteraccuracytest

15OHMMETER.ACCURACYTESTS

Performancechecks

@ \ d

L6. PreferredMethod

OhmmeterAccuracy

AC Voltmeter AccuracY

1OO

Dcvoltmeterinputresistancetest

Pebformancechecks

ACCOMMON.MODEREJECTIONTEST

S24.ACNORMAL.MODEREJECTION

O o ?

Rrr-rrr--r

Model3490APERFOBMANGECHECKS

28AC.VOLTMETEHINPUTIMPEDANCETEST

MU L T I M E T E R h p 3 4 9 O a

@ \ - O @ @ o o

Test Oscillator

6 5 2 a

$38. DC/DCRatioAccuracyTests

Perfohmancechecks

RATI0PEBF0BMANCE0ption 080

+ 100.000

45GPIB.0PEBATIONALCHECK0ption030

S41.AC/DCRatioAccuracyTest

ExternalReferenceInputResistanceTest

Ext Ref Nput Lnput Display Limits Range Voltage

Lo v Ranse

PERFORMANCECHECKSModel3490A

It l l K o

1000kO range

+tll

IiI

Fä il Ir fli

Fj Fl

Ii tti 1üj Li i l

I i , Il

R * ! i t F T

Rf,lIr i5i 1.+ri

It I l L1,1ti

$ 51 .ADJUSTMENTPROCEOURES

Procedures

Adjustment

Powebsupplyadjustment

$57. Referenceadjustments

Model3490AAOJUSTMENTPROCEDURESSectionV

Dczeroadjustments

Dc standardhp- 7a0Bis requiredfor these

69SAMPLE/HO.LDADJUSTMENTS

$66. Ohmmeteradjustments

$75. DielectricAbsorptionAdjustment

Model3490AADJUSTMENTPROCEDURESSectionV

73.0ffsetAdjustment

Dc standardhp- 7a0Bis requiredfor this

Lqe

Aojustmentprocedures

Ratioreferenceadjustments

Orrra

Adjustmentprocedures

ColTect

Perfobmance

Testrecord

LO.V l O V 1 0

Performancetestbecordcontd

001v r 0.oo1v

+ 1 2 . O O O

Ext Ret Fngu V 1 0

Performancetestrecorocontd

50000v Ooooov 120000v

00000v 10.üoo 12.0000v

NON.LISTEDPARTS

Intboduction

Orderinginformation

Proprietaryparts

Description Mfr Mfr PartNumber Designation Code

Otv

Reference HPPartNumber

B l e 6 1 . R e p l o c e q b l eP o r t s

Rcor-@4o Leol-m4ol\

B l e 6 1 . R e p l o c e o b l ep o r t s l C o n t d l

Model

HP Part Numbel

Oty

Reference

B l e 6 1 . R e p l o c e o b l eP o r l s C o n t d

B l e 6 1 . R e p l o c e o b l eP o r t s C o n r d

AI R3A AIR3@

Qty

B l e 6 1 . R e p l o c e o b l eP o r t s C o n t d f

28480 2a4AO

Aterei alnz?

R t s l C o n t d f E p l o c e o b l e

B l e6

Model 3490Ä

B l e 6 1 .R e p l o c e o b l eP o r t s C o n t d

OtyDescription Mfr Code Mfr PartNumber

DesignationReference HPPartNumber

Reeo-sg

B l e 6 1 . R e p l o c e o b l eP q r t s l C o n t d l

Oaa+-rrtt $

DMT4LOON

A5s4 Sli2

B l e 6 1 . R e p l o c e o b l eP o r t s C o n t d

R5ß7

Aoaroassyrehotejuxper

CB a72l

Oty

Cr r?21

?5r-orlo

28aao

Otv

Description Mfr Mfr PartNumber DesignationHPPartNumber Code

2A480

Zroo rzaaAA

B l e 6 1 . R e p l o c e o b l ep o r r s C o n r d

Re*-ooar lil

Orzo-oo+o

Designation

Description Mfr Mfr PartNumber Code

Reference HP Part Numbet otv

B l e 6 1 . R e p l o c e o b l eP o r t s C o n t d

C5 22at

B l e 6 1 . R e p l o c e o b l eP o r r s C o n t d

C8 ?2rl

DrT4LOara

AI3CR8

ModeI34904

T u 2 I l 5 u

O O E B R E a K D O I I N

Caeleriaeon Ottgiitrdrei Isolatii Boardassy

R 2 r

Model Section

Cableribbon

A22API

Heiioi

400

B l e 6 l . R e p l o c e o b l eP o r t s l C o n t d

600

A27RI

Rfxd Cotp IOK OHX IOI L1Y

B l e 6 1 . R e p l o c e o b l eP o r t s l C o n t d

A2ARI

OBD

Z9cl 2 e c t 429C4 29C5

OHn 1trÄ 1/4W

A3IU3

I I P 22K otr lot

I P l2K OHI lot

A32RI

Reference HPPartNumbet oty Description Designation

Mfr Code

A39RA

2211 2211 CB

A34YI

2A4AO 2S4AO

B l e 6 1 . R e p l o c e o b l eP or t s C o n t d

Reference HP Part Numbel

T20/o

IcxssIs assY

B l e 6 1 . R e p l o c e q b l eP o r t s C o n t d

EIlrDtrs PosT assY

284r0 2a+ao 2A480 28480 2g4AO 284aO

Reference

HPPartNumber

Description Mfr Mfr PartNumber

Xo1

Mfr Code Mfr Part Number

Reference HP Part Number Designation

OtvDescription

B l e 6 l . R e p l o c e o b l eP o r t s l C o n t d l

MP7

SectionVI

MP37 MP23

Designator L M P l a MP1B M P l C MP1D MP2 MP3 MP4 MP5 MP6

318x32

29500043

Troubleshootingtrees

Pbeliminarytroubleshooting

ACCESSF0RSERVtCtNG

Powersupplychecks

AZAsemblyExchange

TableT-2. PowerSupplyJumperWires

13DC.ANAL0cCtRCUtTS

DCAmplifierChecks

A N D 0 V L E V E L S O C C U R a T

DCAmplifierSwitchingGircuits

Nlii

I G G E R S C O P E a T a 1 T P K , + S L O P E

37OHMS. Convertebtroubleshooting

3I .INTEGRATOR Troubleshooting

33AC. Convebtertroubleshooting

21A. -to-C0NVERSt0ND CtBCUtTCHECKS

Displaytroubteshooting

Logictboubleshootingsuggestions

59SAMPLE/HOLD.SERVICING

65SAMPTE/HOLD.TROUBLESHOOTINGTREES

ExternalTriggerCircuitGheck

Accesto Sample/HoldGircuits

03490€6528

22000139

03490-006M

O3490-27301

RATIO.TBOUBLESHOOTING

75SCHEMATIC.NOTES

AmplifierZerc0ffset

Truth Table

Logicgatesymbols

+ 5

Truth Table

Alu401 Rexe

SectionVII Model3490A AlphabeticalListingof 34g0A Mnemonics

U 4 o t

Nrsc

IaFeV-pF

Tl-l

= l

Guspb b l

Page

I1Lgji

Iai ott *nn !drp6 ltnt. rync,+.1@

I1glil

Rtl7-r2

+ Input

3ttr . n

@ @@

Ll?Qxl c207c2or

? 1 t 6 1 l 7 + T i + ?

Q208

UiL

T E

YES

AITPK. +

Q2O5 t1 swith

3 6 m s i 4

Ratio INT

0205

R317-1

O2or

0208

LfT

+.JL

RaG

Q9e

See Notes

299A

Ffi

14,iä

?rSlI

LOomsF

1s17-t6

Ov1--t==- -l6oms

R7vl l

Tlrtlt Wath AnDr

Rd 15 ot Altrt. JFuldbo+5V Lm r . tt

Llo

Tlrtlt Wath AnDr

R7l7-r8

Troubl .. hoor A7Ot ?CRIOüa ll

Iub s!!h

#lsriieo,e*l

Eff#ri

I l

DisplayTroubleshootingTree

T9lt

=LJ. L--l

L i l t l

T l

ITa --- it

O 1 o

Ru*rffifc

TEv

NVW

Page

3t,1

Lirlt?lt..it \- toresh@rArur5 aIut1 J

O24 oo24 @24 oo24 9032 oo24 t.o24 n 4 n2.4

Lop

+ 10.oo24

Initiare 6 mre smples

Displaysholdread

+ 60O0.xxOL

LDr s

Tl=l

S l . l

€@CI6@@e#ffi

+ 5 n-s l r

S +

+ i O 5 4 s F

Otuu U.T,J,l,,t-t

Ttj ,o

+5 ms-l

10. Logic Clock TroubleshootingTree

2317-1

$E B?tr+1HHHLE r r r r r r r l

THttttffi

L sl \f -Jt +1 l

+ft$b!too

Llt

L- l l---,.l

Us-l Url

5 a

Jtr2cr

+- zoomsl

\ÄÄ

Llj. -zooms*#ll-+l.l-r

Pulses

Ti1i

Ea . f

1-t.i1

2s17-26

= b3mtl

At7A2

I. J?

Ffi

Gig

Tlu2, a t1u3,Arl

NOI€S

+ 5vr-r

=rF

Th.-l

1o.4ßF

+s-Yml

Figare7-12.RemoteTroubleshootingTree,Option022 2717-28

RtN*16t12

+o.cF

Start

9 0 D- 3 3 8

Hffi3

338r

13. GPIBI/O TroubleshootingTree,Option030 2917-30

Cauil oN . l

Port No V . C

Hp Porl No O Rev . B

Öl--.le

Correcn

A27KI Shoulo 8€ CLOSED.SET SAM

D a

Main CIRC-IIT8OAFO. Shouloae

SET S/H Sayitch to TFACK/HOLD

CABLESCORRECTLYGO. to

9 0 D 3 4 3

T3t17-32

Oft-.*l

HOLD. M€ASURE Voltage AT

Port No . O349O Rev . C

I,l

Hp Fort No -66527 Rev.B

To A2 X E

Iore Sigial G€S High

8Ap-crtot awrcH To rRcx

Eogeof .AIPLIHOU TRIGGCR!G

Tote

RävnG.iir

Ffi.f-L

JüJ

3 f r a

73317-34

3490-0

Hp Pott No.O349O

LOW

P U T

EXT REF TPC

High

P U T TPC

LOW

TPC A13CR6

+ l 0

TPC

G H LOW G H LOW H I G H L O W

16. Ratio TroubleshootingTree

A31 Rearof Instrument

A33

A12 A17 A22 A11 3 or A36 A34 A35 A30

Ral

€ d

I11

111

#Jälslt*tJl=l

+++F+r@a

Jj,i @ @.6r

Rö*et e J l

+ ö

Üä,ierispgglg*@ WEE @D@@@@@ ++++++++f++Evvvvvvvvvvvv

EfEU

18 a Block Diagram

737

REFEBETTCEDESIöTATIOtIS

FP?fä

WüE,Ä,li

CoKno

Ilgt,,a ,,r.i.li

LelQg

Lli-@@@@@@@

Q l

Hovpoverloaoprotectionh

Overloadprotection

A R D

RuorerzV AA

Bootstrap P L I F I E R

T6azt

A M P L I F I E R

Feedbackattenuator

\+l

? z e 1 2 z

391740

$E?

Z r z l

Zl-----l

?o70 f

9i czo1

@$Y@ Y 6ö Ff$$**H++

IRrr5- l .FrrBll- l Pt lP r f

SueeLv +rzV ----d-tr-E +tzv +5V +5v TZV TZV ---b

Lp/0 Al I MArNcrRcurrassEMBLYo34so 6650r +ov +rov

FRoM Sv---*-l---5v

C203 o.33

Zero Detect

1411742

T7v- t7v CR202

XPf*trt*r+9e . E

Faq h-,,dn

Tf,rl

Rblhb-l- --,1

Itu

Ffie

Ott,t

?-rv

V E R T I N G P L I F I E R

F E R E N Cpeo L a R I T YL O G I C

+REFERENCESUPPLY

Figr

F E R E N Cpeo L a R I T YL O C I C

7431744

U3o! ----t

V E R T I N G

Llt ri.ä-i.i Ffi

ß?i-,- *$1,sE1iV

Rrr Nililji

?ääijO * 9sö $

O*. n i!g!?ifiJjscaNBH

Powerfrom -5v---dä-!-- IP*333

3 1 6 t

Siorra

\------lJ

7451

Timingcounter

Stir lT- Il

P .L.iU.B Ll 11

I3g.i

Äiiiirr lir,il..1 Ilir ! o @ @, = T-T

Nne--r LHur

I3Bl,J-r

Rua --I xma

R N O N C L E a R R C U I T

3bEi,?#

Röüärrrr-l

L o

FRoMU6iIä

?5Silij

Otonrä

A N S F E RA N D Z E R O D E T E C T

Tansferenableh F R O MU 9 2

L8d,tshäl 3Yä1..dP

P U T L a RIT Y Storage

E i i + + i +

Pp* @@@@@@@@@@@@

Il J

@@@@@@@*späsw

Lffioi

IlJ**io**l.Io,l

6ffi-l

Fää-.trto-*tot

74917-50

Soue.e,.oloieftil-l

Soupr-Ezro-r-oirfr

Fs-rLErHoLDpi6il-l

Hp PortNo O

+ q r

\ 9 t r l = l

\ R l

Ig t31,.9uIGgARo

Rr,rorHER

220V Toov T20v 240V

TOAa

Ouiro

Regulator

Grppry Optrorr Assr Ozot

+3OV Regulator

5117-s2

+ l 7 v Regulator

3OV Regulator

REV . B

Hp Port No.O349O-66503

BCD

=i33SfTHr-+

Enable

Roaru4oreil

Polaritydisplay

A N N E R a T O R

Polaritydisplay Enable

U4,uro

Scan Decoder

S3l7-s4

Figwe 7-27. SchematicDiagram,Display, A3

Io*F

Ra FE FA FB

Componentside

= E

R C U I TS I D E

Ror..RArEcH,rrr., tfl*l

S l r q r l

Q N a e r , *I .l ,*l ,i , ,ElllRANGEIH**iL

R*.,j#

LFUNcroNl

Ss -s6

LFaN6E-l s4

Test

Ll l

=sÄl---l

+ + 6 D

L-sJ

V, cK+

A6T* .* r*.* *-..u

+tzv ---fre- +rzv r l +5v --+r5- +5v

Converteramplifier

Oot

Attenuator

+ r 7

Filter

Figwe 7-29. SchematicDiagram,AC Converter,A6

S7l7-s

Nc corvepreR ourPUT1

Ofqlrod 06t90-O999-l

Drluod O6t9O-20999

UeacpalpueHuoll3as

Flt Bl,,J.li,i Vrx Norlrr,rn CNn.Norr vH

Ei-tr

Ifl3?5fö*co,c

GttornrvsnHounor Rsnxo

U3t3NltHO33N3U3J3U

Arn8rg Crlerueqcs Surq6 Urur8erq RelJouoJrV 0vLl6s

LN3UUnC l3unos

Ssoucv 39N lmdNt

42242

? ? T

A22Al

Rxrnrr

1M1 ASSEMBLY 3äYäiäT?lTl-?.1..i

Fff.ItTrsGooo +l--.r

+l8oyJl,flylo

SAMPLE/ Hold Triggercircuit

Tl,,t1

+f-!-l-tr-ourcuaRo

7411142

Wro

Ro ooroorrr coNNEcroRJ6 Ro *.or. ,*r* coNNEcroRJ7

Ur-l

L J J l

Älll

5 a

Q U E N T I ALO G I C

ÄX?,3,.o

LEoR Eon Fil!Täläf

Freque

+-n

Logtc Clock Frequencydoublerdelay

Data Multiplexers

Outguard

DAraFLAG

# , . , J

9 \ I C E N I a N ri fr. F

2eI

W S H I F TR E G I S T E R S

I G a N E

+5vr---1i1+4

Guaro

Zfu*-rrot

+ 4 l

Oi---qo

74317-64

7 a

At7

Oo-1 Al2 Hp porttJo,03490-66512

LOCAL/ Remote FLIP- Flop

+ s

LO REMoTEnruruurrcraron

LOCAL/REMOTE

= r

RHs tl su31sr93u

91 .-Ct

Lockdelay

AJtlilo-*il1.iI

FlIto*.- -7u u5

NBId

\ .,- I \ Onr9nvu0 rdtIlnn-u3x3

Rns+

Ouvngmo l,ssv

Z r

Hp Port No

To A2 C D E F H J K L

L8 PRbou%u

F8fi8

14,0o*%ÄäuJJii

T8 iäB?i

46.4 K

R c * o lI l r g S

If U8 is BAD.OUTPUTWAVEFORMS

Will 8E Loadeddown

Rt\u

?? l9Li9i.-.?

747l7-68

? * t o RrreenrroR

Porf No . O349O Rev . C

U l H

€l-----19

TABu?,.ffiIi

Ori

Iäo*,j.,lj!,j

O 1

A L I F I E R M U L T I P L E X E R

Bs-u

M P L E /H O L D T R I G G E R CI RC U I T S

Hmtb

?6Tr%r,i

?.46,f

74917-70

OEo o r a o r B orc o r o o t M

Jil

CRs

SDo

To S/H Logic

I N E

LOCAL/REMOTE $ Ection Aage Clocks 5 Lines

Dislay

COPYRIGHTt973 by Hewlett Packaro

Ouoorn REcErw

36.BlockDiagram,3490AGPIBVOCircuits 7117-72

FC Company

Hp Porr N 0 3 4 9 0 6 6 5 3 6 Rev a

L24-----r3-l Or5

Hp Port N o . O 3 4 9 O 6 6 5 3 4 R e v .A

N D

RnvH ornv H Or6rnrv CucxJ Rvu . Hccr

Tot

Orurr9iorrrol98rfiilV

RvrrxrJNorroNnr Rfillj

Tt lrstl3ssv

Ertv Rzr Slinur

Sosr

83x3ldlrln$l

S K

RaI ,tuf,r 3+r7v

Uui-,f +sv

Tzv--Le f -rzv

?,il9Bälooo

O r

+Fol

U 1

R l

?oti.lä?fr?ox?Ei6q*1Eefi&x?ot

Port No

Rl?ulF5-ß-olqrroil

Ä33a

Uu +sv

ETGpr 03490

Lre a

Ä3a

GLA

HRsr o

RfbÄiÄÄ 2 -ixaorJ

7517-76

? l

Or.nroro Orrl assv 2 l

L3-JrIt TLr.sl-------l

432

Ri------l

Hp porr No.03490-66532Rev a

22LEoP-rJi,19#E8ffi0 22fr,.#.!äi$o LsRe--1i-,r

Lrrx i--=

20A%ll?i8*o1lg9lRor-oos---Lrs-r-oosl

20 loo.tfliloX!3VotoLRMrl

I I z

Iä.ggx3!.zz

Ooorf

Fruox

Roro-r-,@

CvvH r

Ilo Sa-oosl.J?il!.31..Ä.OZ

Ilr

9I3?ü?591.ZZ

Nzr Rnzr RE+

R K o

TT----l

Hp Port No.oi49o-6653t RevA

CR3 CR5

Wououvngrno

Oo-1--5

Rvvr

+lvvH Vrvossv Ovvx-+

O L a T E D P O $ / E RS U P P L I E S

+rzv1

+ 5 V r

+ l z v l

LsoroH

Your

Ztisv Orur

IsoroH L n OZssv Rorol

L0Nvl3 33Nln0ls

SruvdroN Orlsr

N0rrcn00urNll

JzztyostorJzypxJ

TluzvtJzv Inzvlrncrrc Ppv Pue gluzv ot

Zzlosro

Jeu

TlzGszzov

O ö t

Äää

Ii ä ä i

Eää3

Arnorg LLVrueroerg Clpuaqcs Reslquassv.plgglLoV!Z!oNpueol

A8dqdw

Burur5

ÄffiäHi!,äffT1Hiä1s,äTffff-nill-,gl

Toot lsn tosütünlYrnilYw

LodrlaH

Owl v N n l v r r n u r u s

Pulsl

ÄJnuf

LqunloC IEIuqcaI

Opuntas

Iutdd!q\Nf

L a a J o J d

Sttvs ? Tctuts s3crJjo Otrriln Srlvls

9er rtl9

99.68r

VovNvc

RrlanD

Leiol

Rturtt

Lvulsnv-vr

C3rNrudNt

OüvxgvdEt

06rt0-il006