|

|

| Freescale Semiconductor, Inc. | |||

|

|

|

| Operating Instructions | ||

|

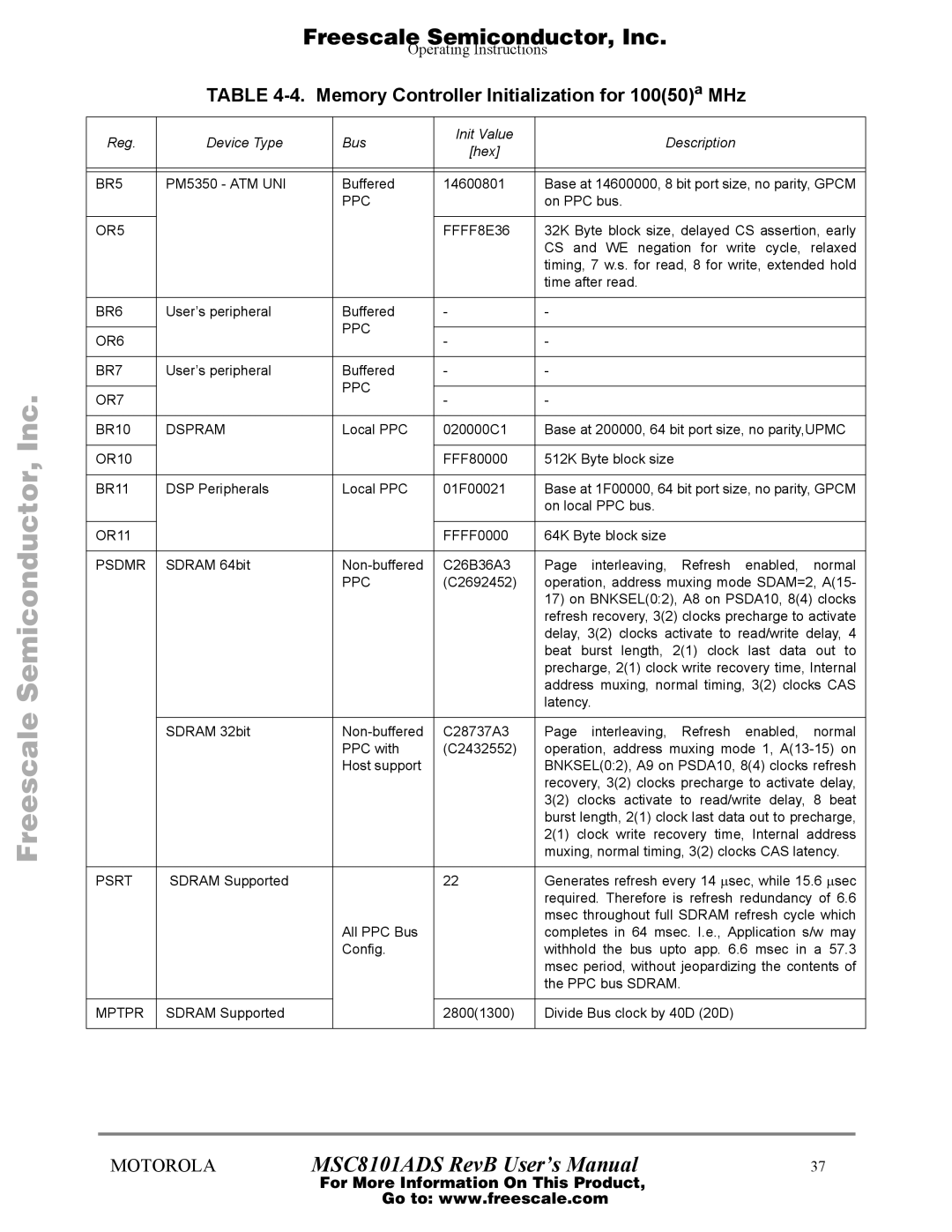

| TABLE | ||||

| Reg. | Device Type |

| Bus | Init Value | Description |

|

| [hex] | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| BR5 | PM5350 - ATM UNI |

| Buffered | 14600801 | Base at 14600000, 8 bit port size, no parity, GPCM |

|

|

|

| PPC |

| on PPC bus. |

|

|

|

|

|

|

|

| OR5 |

|

|

| FFFF8E36 | 32K Byte block size, delayed CS assertion, early |

|

|

|

|

|

| CS and WE negation for write cycle, relaxed |

|

|

|

|

|

| timing, 7 w.s. for read, 8 for write, extended hold |

|

|

|

|

|

| time after read. |

|

|

|

|

|

|

|

| BR6 | User’s peripheral |

| Buffered | - | - |

|

|

|

| PPC |

|

|

| OR6 |

|

| - | - | |

|

|

|

| |||

|

|

|

|

|

|

|

| BR7 | User’s peripheral |

| Buffered | - | - |

Inc. |

|

|

| PPC |

|

|

OR7 |

|

| - | - | ||

|

|

| ||||

|

|

|

|

|

| |

BR10 | DSPRAM |

| Local PPC | 020000C1 | Base at 200000, 64 bit port size, no parity,UPMC | |

|

| |||||

|

|

|

|

|

|

|

Semiconductor, | OR10 |

|

|

| FFF80000 | 512K Byte block size |

|

|

|

|

|

| |

BR11 | DSP Peripherals |

| Local PPC | 01F00021 | Base at 1F00000, 64 bit port size, no parity, GPCM | |

|

| |||||

|

|

|

|

|

| on local PPC bus. |

|

|

|

|

|

|

|

| OR11 |

|

|

| FFFF0000 | 64K Byte block size |

|

|

|

|

|

|

|

| PSDMR | SDRAM 64bit |

| C26B36A3 | Page interleaving, Refresh enabled, normal | |

|

|

|

| PPC | (C2692452) | operation, address muxing mode SDAM=2, A(15- |

|

|

|

|

|

| 17) on BNKSEL(0:2), A8 on PSDA10, 8(4) clocks |

|

|

|

|

|

| refresh recovery, 3(2) clocks precharge to activate |

|

|

|

|

|

| delay, 3(2) clocks activate to read/write delay, 4 |

|

|

|

|

|

| beat burst length, 2(1) clock last data out to |

|

|

|

|

|

| precharge, 2(1) clock write recovery time, Internal |

|

|

|

|

|

| address muxing, normal timing, 3(2) clocks CAS |

Freescale |

|

|

|

|

| latency. |

|

|

|

|

|

| |

| SDRAM 32bit |

| C28737A3 | Page interleaving, Refresh enabled, normal | ||

|

|

| ||||

|

|

|

| PPC with | (C2432552) | operation, address muxing mode 1, |

|

|

|

| Host support |

| BNKSEL(0:2), A9 on PSDA10, 8(4) clocks refresh |

|

|

|

|

|

| recovery, 3(2) clocks precharge to activate delay, |

|

|

|

|

|

| 3(2) clocks activate to read/write delay, 8 beat |

|

|

|

|

|

| burst length, 2(1) clock last data out to precharge, |

|

|

|

|

|

| 2(1) clock write recovery time, Internal address |

|

|

|

|

|

| muxing, normal timing, 3(2) clocks CAS latency. |

|

|

|

|

|

|

|

| PSRT | SDRAM Supported |

|

| 22 | Generates refresh every 14 ∝sec, while 15.6 ∝sec |

|

|

|

|

|

| required. Therefore is refresh redundancy of 6.6 |

|

|

|

|

|

| msec throughout full SDRAM refresh cycle which |

|

|

|

| All PPC Bus |

| completes in 64 msec. I.e., Application s/w may |

|

|

|

| Config. |

| withhold the bus upto app. 6.6 msec in a 57.3 |

|

|

|

|

|

| msec period, without jeopardizing the contents of |

|

|

|

|

|

| the PPC bus SDRAM. |

|

|

|

|

|

|

|

| MPTPR | SDRAM Supported |

|

| 2800(1300) | Divide Bus clock by 40D (20D) |

|

|

|

|

|

|

|

MOTOROLA | MSC8101ADS RevB User’s Manual | 37 |

For More Information On This Product,

Go to: www.freescale.com