MSC8101 ADS

MSC8101ADS RevB User’s Manual

Contents

ATM on LD14

BOM

Freescale Semiconductor, Inc

List of Figures

Viii

List of Tables

Freescale Semiconductor, Inc

Introduction

Abbreviations’ List

Related Documentation

Specification

MSC8101ADS Specifications

Characteristics Specifications

ADS Features

Freescale Semiconductor, Inc

Semiconductor, Inc

Hardware Preparation

MSC8101ADS Top Side Part Location diagram

Setting The Core Supply Voltage Level

Setting MODCK13 For Initial PLLs’ Multiplication Factor SW9

Setting HReset Configuration Source

Host I/F Operation

OnCE Connection Scheme

Host System Debug Scheme B

Stand Alone Operation

JTAG/OnCE Connector P6

34 +5V Power Supply Connection

P6 JTAG/OnCE Port Connector

Host I/F Connector P4

Terminal to MSC8101ADS RS-232 Connection

P4 Host I/F Connector

38 10/100-Base-T Ethernet Port Connection

Flash Memory Simm Installation

Flash Memory Simm Insertion

Emulator Enable EE SW2

Host I/F Setting SW1

Abort Switch SW3

Soft Reset Sreset Switch SW4

Data Bus Width Setting SW5 & SW6

Hard Reset Hreset Switch SW7

Power-On Reset Switch Preset SW8

Configuration Switch SW9

Boot Mode Select SW10

Available Clock Mode Setting

Modck

CPM

431 JP1 DLL Disable

Software Options Switch SW11

Jumpers

432 JP2 Clock Buffer Set

436 JP6,JP7 MIC Enable

433 JP3 50 Ohm Enable

437 JP9 5V power supply for Codec

434 JP4 VPP Source Selector

LEDs

Fast Ethernet Clsn Indicator LD5

Ethernet Link Indicator LD4

ATM RX Indicator LD6

ATM TX Indicator LD7

MSC8101’s Registers’ Programming

SIU Registers’ Programming

System Initialization

Memory Controller Registers Programming

Memory Controller Initialization for 10050a MHz

Memory Controller Initialization for 10050a MHz

Mbmr

Power- On Reset

Reset & Reset Configuration

Power On Reset Configuration

Manual Hard Reset

Hard Reset Configuration Word

Summary Reset Configuration Schemes

IRQ2

Manual Soft Reset

Clock Generator

Local Interrupter

Chip Select Generator

Bus Buffering

MSC8101ADS Chip Select Assignments Bus Timing Machine

Synchronous Dram Bank

MHz Sdram Mode Register Programming

Sdram Programming

Sdram

Cycle Type \ Flash Delay nsec

Flash Memory Simm

Sdram Refresh

Flash Programming Voltage

Flash Simm Connection Scheme

Communication Ports

MSC8101 I/O Ports/Name

Ports Function Enable

582 100/10 Base T Port

581 ATM Port

CS4221 Programming

Audio Codec

5831 CS4221 Programming

CS4221 Programming

584 T1/E1 Ports

585 RS232 Ports

Host I/F

Host I/F Interconnect signals

DMA off-board tool

Board Control & Status Register Bcsr

BCSR0 Board Control / Status Register

BCSR0 Description

BIT Mnemonic

PON ATT DEF Hostcsp

BCSR0 Description

10. BCSR1 Description

BCSR1 Board Control / Status Register

PON ATT DEF Atmrst

10. BCSR1 Description

Fethien

Fethrst

11. Peripheral’s Availability Decoding

12. BCSR2 Description

BCSR2 Board Control / Status Register

13. Flash Presence Detect 75 Encoding

12. BCSR2 Description

14. Flash Presence Detect 41 Encoding

BCSR3 Board Status Register

15. BCSR3 Description

17. External Tool Revision Encoding

16. EXTOOLI03 Assignment

18. ADS Revision Encoding

Engineering

PPC Bus Memory Map

MSC8101ADS Memory Map

FE000000 Ffffffff

MSC8101ADS Memory Map

FF000000 Ffffffff

FF800000 Ffffffff

ADS Power Scheme

Power rails

711 5V Bus

Off-Board Application Maximum Current Consumption

712 3V Bus

713 5V Bus

Appendix a MSC8101 Bill of Material

Table A-1. MSC8101ADS Bill Of Material

A1 BOM

Freescale

Inc

Inc

Dale

Freescale

Semiconductor

Freescale Semiconductor, Inc

Appendix B Support Information

B11

Interconnect Signals

Table B1-2. P1 System Expansion Interconnect Signals

TSTAT0

GND

TSTAT1

TSTAT2 TSTAT3 TSTAT4 TSTAT5

Damage to the PM5350 ATM UNI

Clkx

EXPD1

EXPD0

EXPD2

EXPD3

EXPCTL0

Table B1-3. P2 CPM Expansion Interconnect Signals

B12 MSC8101ADS’s P2 CPM Expansion Connector

SCC1RXD PD30

SPIMOSIPD17

SPICLKPD18

Hwrds

PD7

Atmrsoc PA27

Atmtsoc PA29

Atmrfclk

Atmrca PA26

ATMRXD6 PA16

ATMRXD7 PA17

ATMRXD5 PA15

ATMRXD4 PA14

Fethrxer PB28

Fethtxen PB29

Fethcol PB27

Fethcrs PB26

HD1

HD0

HD2

HD3

Fethmdc PC13

Atmfclk PC26

PC7

Fethmdio PC12

PC6

SMCTX1PC5

Table B1-4. P3 ISP Connector Interconnect Signals

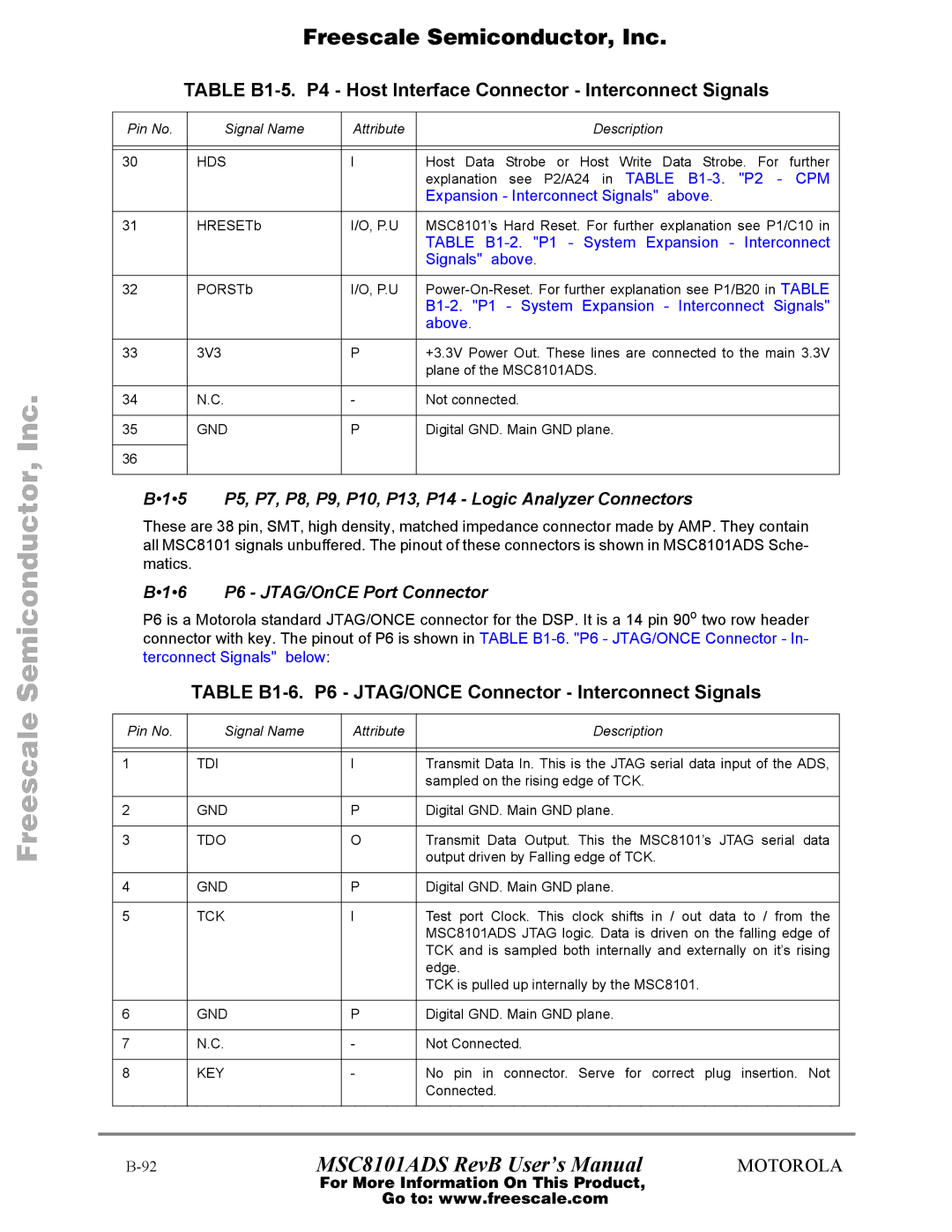

B14 P4 Host Interface Connector

B13

HA1 HA2 HA3 HCS1

HD1 HD2 HD3 HD4 HD5 HD6 HD7 HD8 HD9

Hack

Hreq

B15 P5, P7, P8, P9, P10, P13, P14 Logic Analyzer Connectors

Table B1-6. P6 JTAG/ONCE Connector Interconnect Signals

B16

HDS

B17 P12 Ethernet Port Connector

Table B1-7. P12 Ethernet Port Interconnect Signals

B18 P15,P16 SMB Connectors

B19 P17,P18 Double RJ45 T1/E1 Line Connectors

B111 P20,P22,P23,P25 RCA Jack Connectors

B110 P19,P21,P24 Stereo Phone Jack Connectors

Table B1-11. P27B Interconnect Signals

Table B1-10. P27A Interconnect Signals

B112 P26 5V Power Supply Connectors

B113 P27A,B RS232 Ports’ Connectors

Freescale Semiconductor, Inc

Appendix C Program Information

Freescale Semiconductor, Inc

C11 First Include File

Logic Equations

C12 Second Include file

C13 Main File

Constant EE45HOLDVALUE

Constant SHIFTLENGTH= Length of HRD/HRW Delay Shifter SIZE0

Constant SIZE1

Constant

HDIMDEN~ Host SW Enable RSTCNF~ Output

Constant TCPCDEFAULT0 Constant TCPCDEFAULT1

SRESET~

HRESET~ Bidir

SPARE1 Output

SBOOTENOUT~

HDIEN~

HRRQEN~

WDTIMER2

WDTIMER1

WDTIMER3

WDTIMER4

Resets Cleartowdctrl

Eepromenable

BCSR1 SBOOTEN~

Scndcfgbyteread Thirdcfgbyteread Fourthcfgbyteread

IRQ0

BCSR3

BCSR1PONDEF0..SIZE1

BCSR3PONDEF0..SIZE3

Begin Defaults

END Defaults

BCSR0 BCSR0PONCONST0..5

EEDPONDEFAULT,RSV37PONDEFAULT

Else

END if END Generate

Regularpoweronreset = RPORI~ == Regularponresetactive

EE Pins

PSDVAL~ = Opndrnvcc

END if

If !HDSP then Hdiwr =

If Hdds then

Else Hdiwr =

END if Else

Elsif MPCWRITEBCSR4 then

Elsif MPCWRITEBCSR1 then

Elsif MPCWRITEBCSR5 then

Elsif MPCWRITEBCSR6 then

SIGNALLAMP1~ Elsif MPCREADBCSR1 then

If MPCREADBCSR0 then

Elsif MPCREADBCSR3 then

SRESET~ =

HRESET~ =

Elsif Firstcfgbyteread then

Elsif Scndcfgbyteread then

Then SIGLAMP1OUT~

Then SIGLAMP0OUT~ = GND Else

Else SIGLAMP1OUT~

END if If !T1234EN~ & FETHIEN~ then

116

END if Drive Poreset Impulse Reconfig Using BCSR4

Watchdog for Auto Reconfiguration

MODCK1-3 Driven

118