Freescale Semiconductor, Inc.

|

| Freescale Semiconductor, Inc. |

|

| |||||||

|

|

| Functional Description |

|

|

|

|

| |||

|

| TABLE |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ADS |

|

| DMA Ext. | Possible | ||

|

|

|

|

|

|

| Tool | Collision | |||

|

|

|

|

|

|

|

|

|

| ||

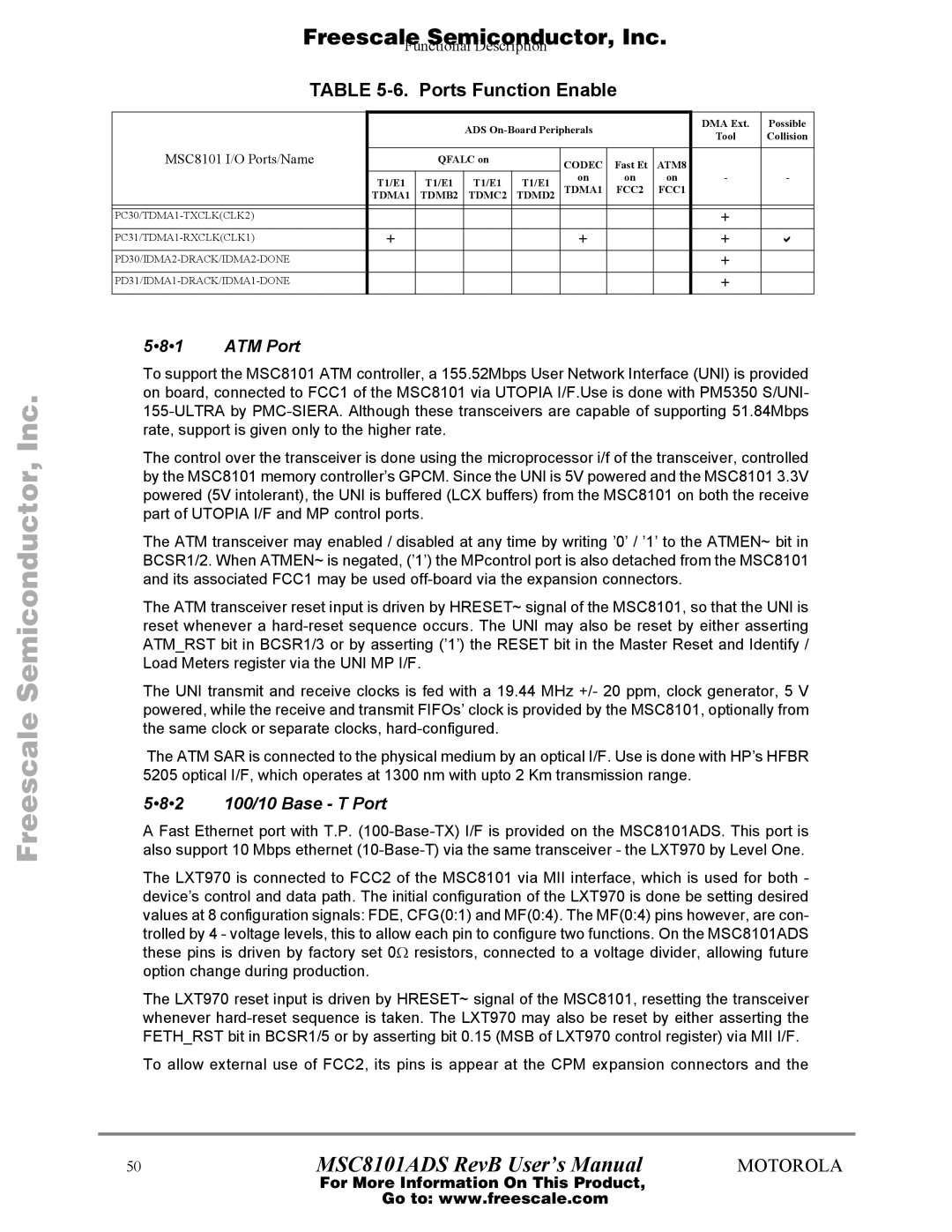

MSC8101 I/O Ports/Name |

|

|

|

|

|

|

|

| |||

| QFALC on |

| CODEC | Fast Et | ATM8 |

|

| ||||

|

|

| T1/E1 | T1/E1 | T1/E1 | T1/E1 | on | on | on | - | - |

|

|

| TDMA1 | FCC2 | FCC1 |

|

| ||||

|

|

| TDMA1 | TDMB2 | TDMC2 | TDMD2 |

|

| |||

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| + |

| ||

| + |

|

|

| + |

|

| + |

| ||

|

|

|

|

|

|

|

| + |

| ||

|

|

|

|

|

|

|

| + |

| ||

5•8•1 | ATM Port |

|

|

|

|

|

|

|

|

|

|

To support the MSC8101 ATM controller, a 155.52Mbps User Network Interface (UNI) is provided on board, connected to FCC1 of the MSC8101 via UTOPIA I/F.Use is done with PM5350 S/UNI-

The control over the transceiver is done using the microprocessor i/f of the transceiver, controlled by the MSC8101 memory controller’s GPCM. Since the UNI is 5V powered and the MSC8101 3.3V powered (5V intolerant), the UNI is buffered (LCX buffers) from the MSC8101 on both the receive part of UTOPIA I/F and MP control ports.

The ATM transceiver may enabled / disabled at any time by writing ’0’ / ’1’ to the ATMEN~ bit in BCSR1/2. When ATMEN~ is negated, (’1’) the MPcontrol port is also detached from the MSC8101 and its associated FCC1 may be used

The ATM transceiver reset input is driven by HRESET~ signal of the MSC8101, so that the UNI is reset whenever a

The UNI transmit and receive clocks is fed with a 19.44 MHz +/- 20 ppm, clock generator, 5 V powered, while the receive and transmit FIFOs’ clock is provided by the MSC8101, optionally from the same clock or separate clocks,

The ATM SAR is connected to the physical medium by an optical I/F. Use is done with HP’s HFBR 5205 optical I/F, which operates at 1300 nm with upto 2 Km transmission range.

5•8•2 100/10 Base - T Port

A Fast Ethernet port with T.P.

The LXT970 is connected to FCC2 of the MSC8101 via MII interface, which is used for both - device’s control and data path. The initial configuration of the LXT970 is done be setting desired values at 8 configuration signals: FDE, CFG(0:1) and MF(0:4). The MF(0:4) pins however, are con- trolled by 4 - voltage levels, this to allow each pin to configure two functions. On the MSC8101ADS these pins is driven by factory set 0Ω resistors, connected to a voltage divider, allowing future option change during production.

The LXT970 reset input is driven by HRESET~ signal of the MSC8101, resetting the transceiver whenever

To allow external use of FCC2, its pins is appear at the CPM expansion connectors and the

50 | MSC8101ADS RevB User’s Manual | MOTOROLA |

For More Information On This Product,

Go to: www.freescale.com