Section 6 Status Report

6.2Status Registers Specified by IEEE488.2

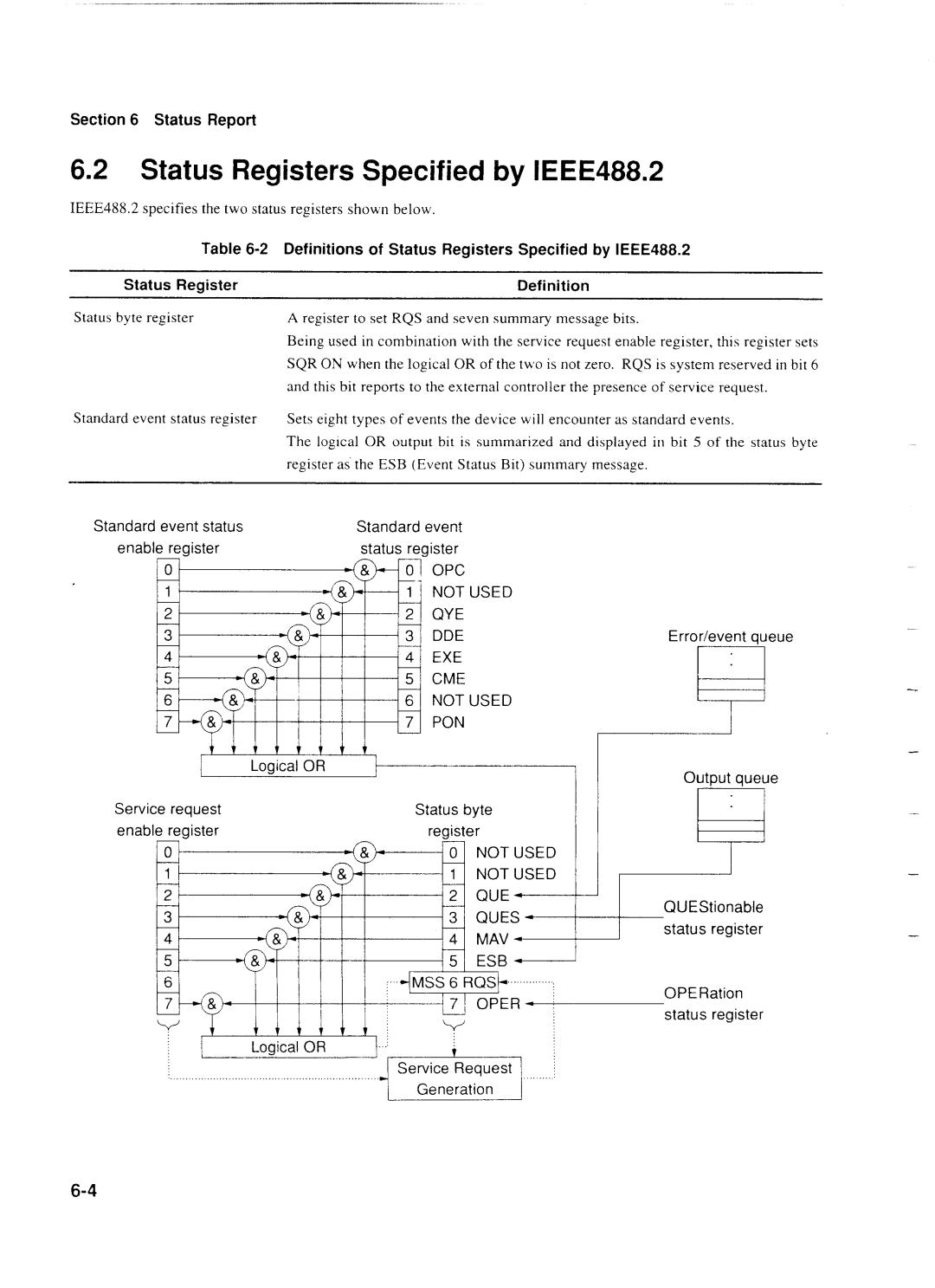

IEEE488.2 specifies the two status registers shown below.

Table 6-2 Definitions of Status Registers Specified by IEEE488.2

Status Register

Status byte register

Definition

A register to set RQS and seven summary message bits.

Being used in combination with the service request enable register, this register sets SQR ON when the logical OR of the two is not zero. RQS is system reserved in bit 6 and this bit reports to the external controller the presence of service request.

Standard event status register Sets eight types of events the device will encounter as standard events.

The log~calOR output bit is summarized and displayed in bit 5 of the status byte register as' the ESB (Event Status Bit) summary message.

Standard event status | Standard event | |

enable register | status register | |

| OPC | |

1 | NOT USED | |

- |

| QYE |

2 | . 2 | |

DDE

EXE

CME

NOT USED

PON

Service request | - | Status byte | 1 | |

- | - |

|

| |

enable register |

| register | 1 | |

jO/ |

|

| NOTUSED | |

1 |

|

|

|

|

- |

| 2 | QUE |

|

2 |

|

| ||

- | QUES |

| ||

3 |

| |||

- |

|

|

|

|

4 |

|

|

|

|

- |

|

|

|

|

5 . | 5- |

| ESB |

|

- |

|

|

|

|

Logical OR | . . |

| |

|

| ||

. . .. . ... ........ ..... . . ....... ... ............. .. ..... . . | Service Request | .. .... | |

Generation | |||

|

|

Errorlevent queue

I

Output queue

F

status register

OPERation status register