6.2 Status Registers Specified by

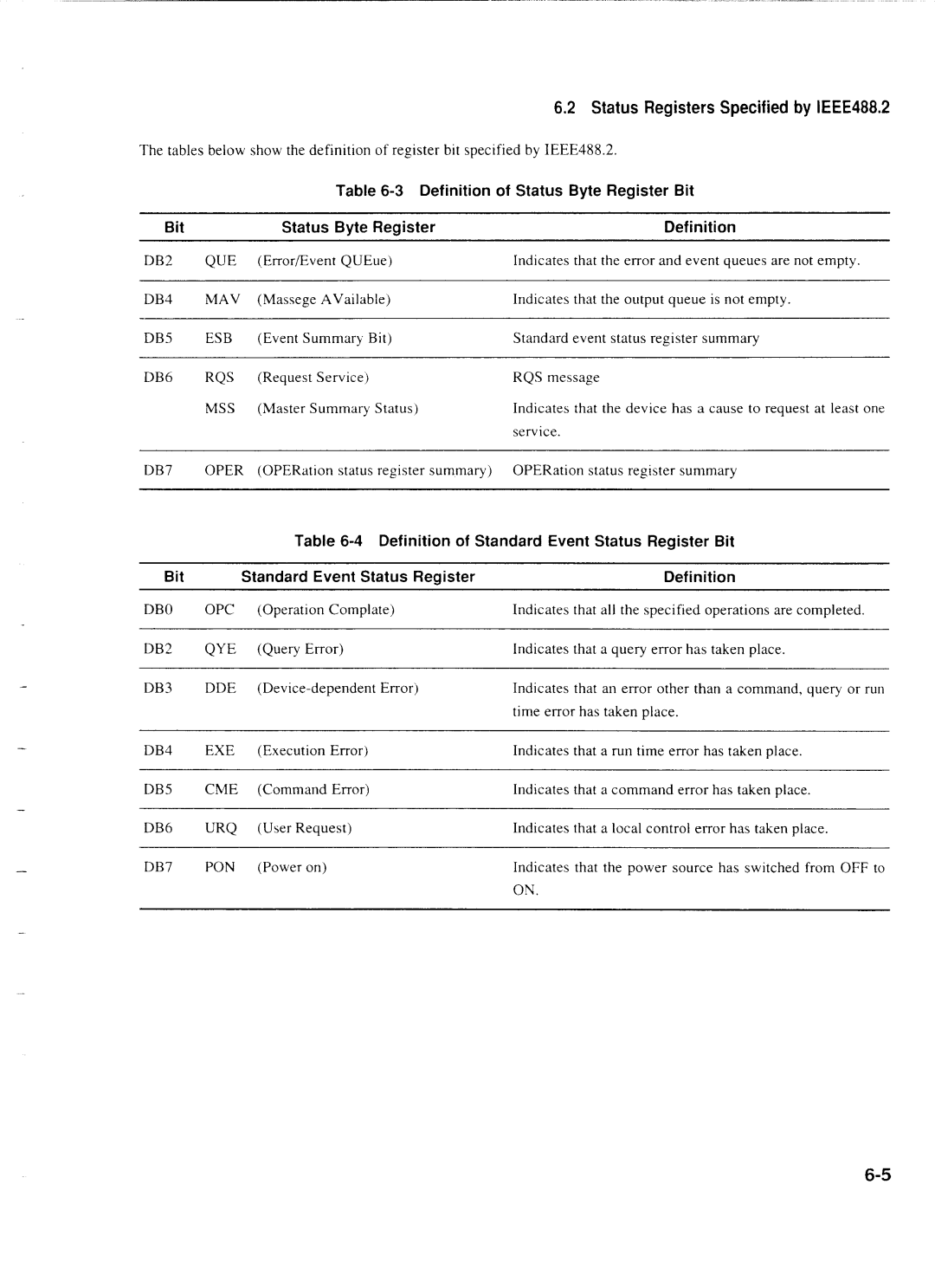

The tables below show the definition of register bit specified by IEEE488.2.

|

| Table | |

Bit |

| Status Byte Register | Definition |

DB2 | QUE | (ErrorEvent QUEue) | Indicates that the error and event queues are not empty. |

DB4 | MAV | (Massege Available) | Indicates that the output queue is not empty. |

DB5 | ESB | (Event Summary Bit) | Standard event status register summary |

DB6 | RQS | (Request Service) | RQS message |

| MSS | (Master Summary Status) | Indicates that the device has a cause to request at least one |

|

|

| service. |

DB7 | OPER | (OPERation status register summary) | OPERation status register summary |

|

| Table | |

Bit | Standard Event Status Register | Definition | |

DBO | OPC | (Operation Complate) | Indicates that all the specified operations are completed. |

DB2 | QYE | (Query Error) | Indicates that a query error has taken place. |

DB3 | DDE | Indicates that an error other than a command, query or run | |

|

|

| time error has taken place. |

DB4 | EXE | (Execution Error) | Ind~catesthat a run time error has taken place. |

DB5 | CME | (Command Error) | Indicates that a command error has taken place. |

DB6 | URQ | (User Request) | Indicates that a local control error has taken place. |

DB7 | PON | (Power on) | Indicates that the power source has switched from OFF to |

|

|

| ON. |