Figure 5-41: Block address

•To access a particular memory location, the CPU transforms an effective address into a physical address using one of the following address translation mechanisms.

•Real mode address translation, where address translation is disabled. The physical address is the same as the effective address.

•Block address translation, which translates the effective address corresponding to a block of 128 KB to 256 MB size.

•Page address translation, which translates a

The translation mechanism is chosen based on the type of effective address (page or block) and settings in the processor Machine State Register (MSR).

Settings in the MSR and page, segment, and block descriptors are used in implementing access control. The following describes the MSR, page descriptor, segment descriptor, and block descriptor structures, and identifies fields that are relevant for implementing access control.

5.5.2.3.1Machine State Register

The Machine State Register (MSR) is a

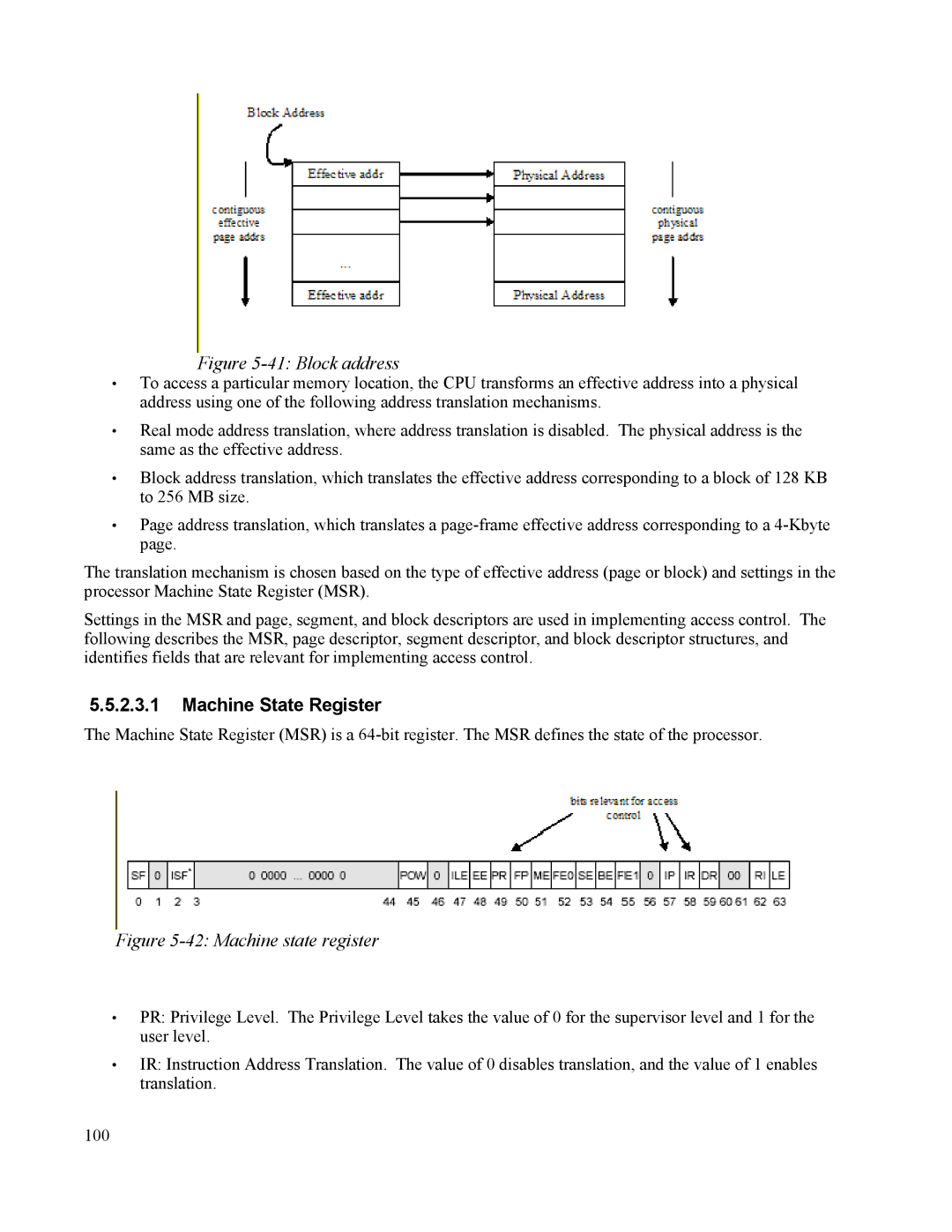

Figure 5-42: Machine state register

•PR: Privilege Level. The Privilege Level takes the value of 0 for the supervisor level and 1 for the user level.

•IR: Instruction Address Translation. The value of 0 disables translation, and the value of 1 enables translation.