5.5.2.1.1Segmentation

The segmentation unit translates a logical address into a linear address. A logical address consists of two parts: a 16 bit segment identifier called the segment selector, and a

Each segment is represented by an

From the perspective of hardware security access, both GDT and LDT are equivalent. Segment descriptors are accessed through their

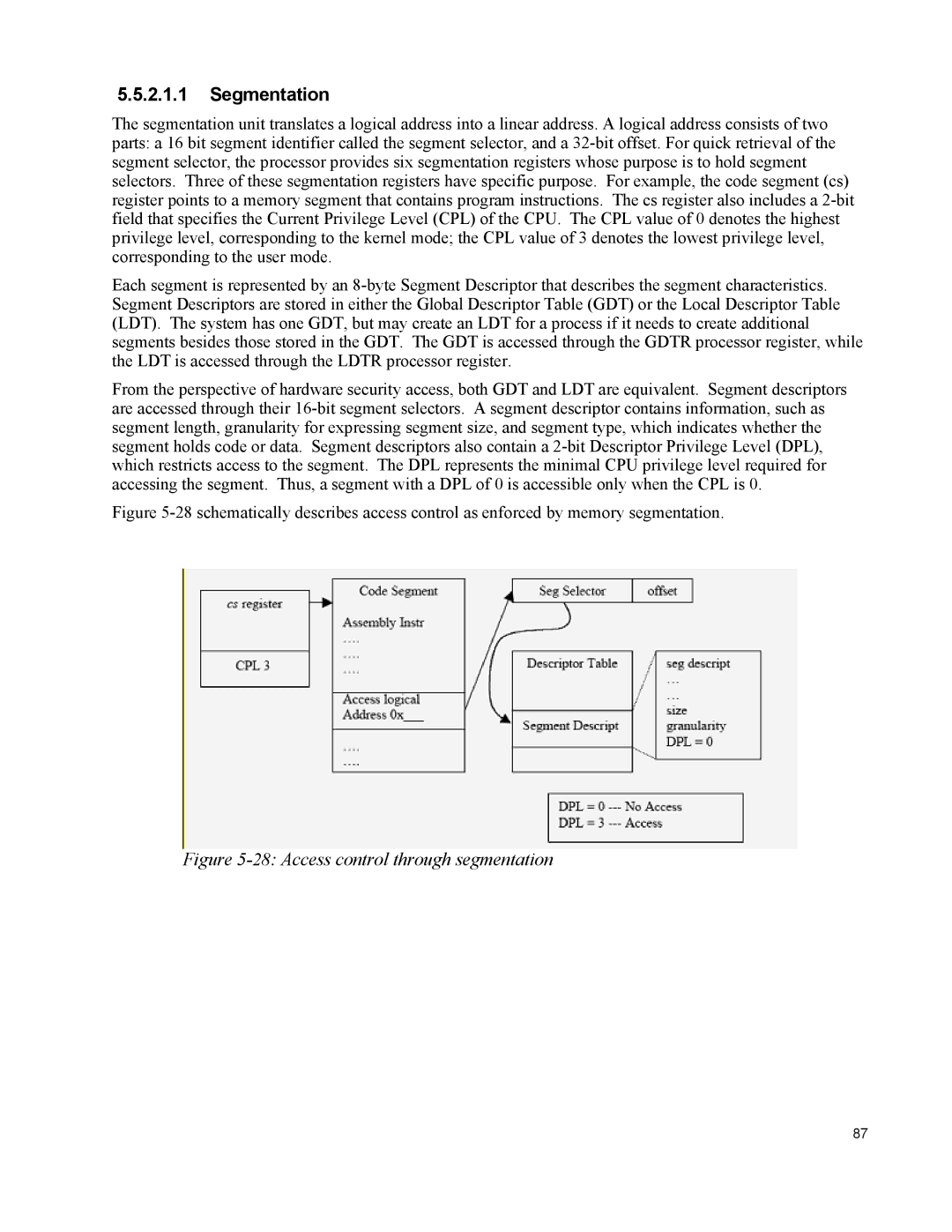

Figure 5-28 schematically describes access control as enforced by memory segmentation.

Figure 5-28: Access control through segmentation

87