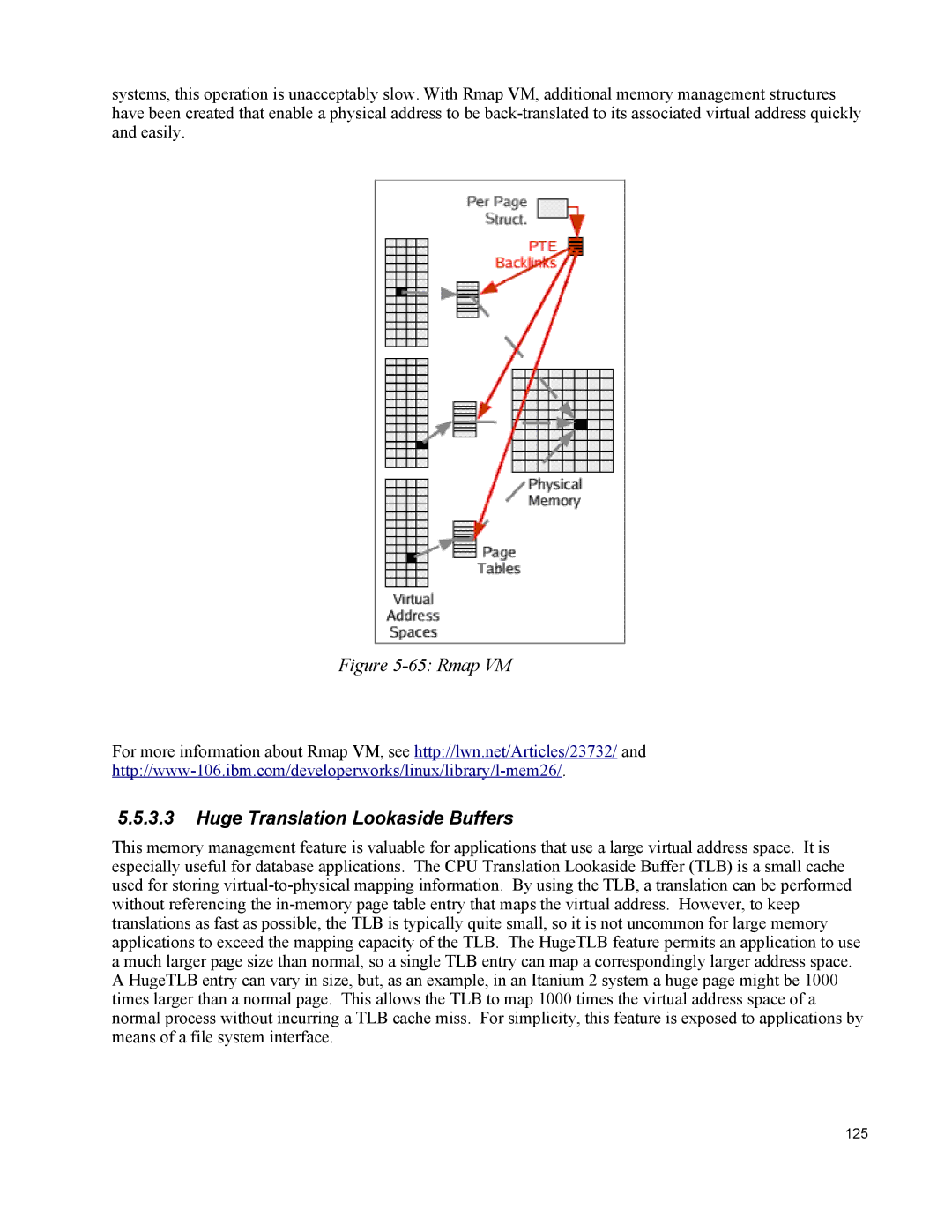

systems, this operation is unacceptably slow. With Rmap VM, additional memory management structures have been created that enable a physical address to be

Figure 5-65: Rmap VM

For more information about Rmap VM, see http://lwn.net/Articles/23732/ and

5.5.3.3Huge Translation Lookaside Buffers

This memory management feature is valuable for applications that use a large virtual address space. It is especially useful for database applications. The CPU Translation Lookaside Buffer (TLB) is a small cache used for storing

125