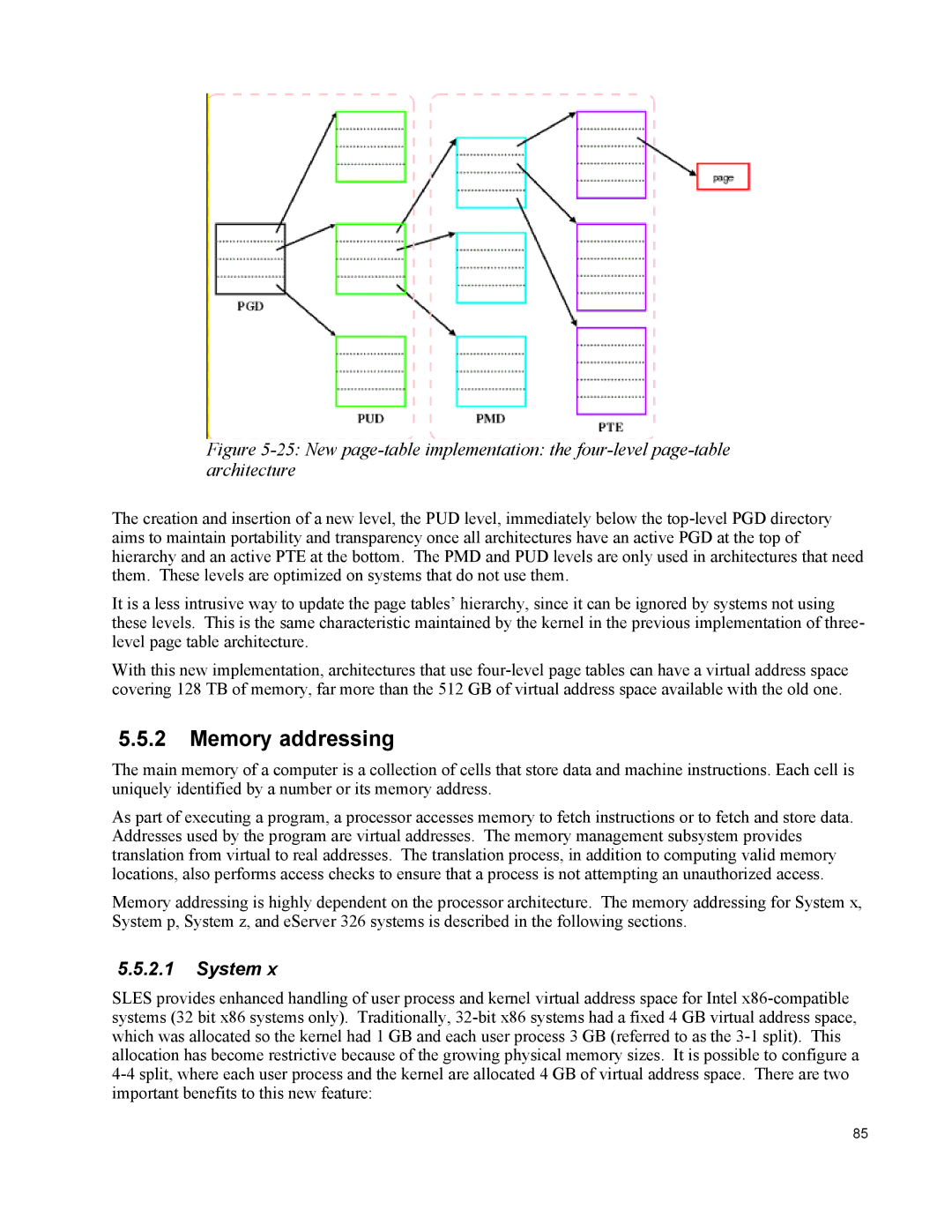

Figure 5-25: New page-table implementation: the four-level page-table architecture

The creation and insertion of a new level, the PUD level, immediately below the

It is a less intrusive way to update the page tables’ hierarchy, since it can be ignored by systems not using these levels. This is the same characteristic maintained by the kernel in the previous implementation of three- level page table architecture.

With this new implementation, architectures that use

5.5.2Memory addressing

The main memory of a computer is a collection of cells that store data and machine instructions. Each cell is uniquely identified by a number or its memory address.

As part of executing a program, a processor accesses memory to fetch instructions or to fetch and store data. Addresses used by the program are virtual addresses. The memory management subsystem provides translation from virtual to real addresses. The translation process, in addition to computing valid memory locations, also performs access checks to ensure that a process is not attempting an unauthorized access.

Memory addressing is highly dependent on the processor architecture. The memory addressing for System x, System p, System z, and eServer 326 systems is described in the following sections.

5.5.2.1System x

SLES provides enhanced handling of user process and kernel virtual address space for Intel

85