FrameSaver� DSL

Copyright E 2000 Paradyne Corporation All rights reserved

Contents

Configuration Options

Operation and Maintenance

Troubleshooting

Setting Up Network Health for FrameSaver Devices

Index

About This Guide

Purpose and Intended Audience

Document Organization

Test procedures

Troubleshooting. Provides device problem resolution

Alarm, and other information, as well as troubleshooting

Setting Up OpenLane for FrameSaver Devices. Identifies

Product-Related Documents

To indicate a hyperlink to additional information

When viewing this manual online. Click on

Conventions Used

Highlighted text

About the FrameSaver DSL Unit

System Overview

System Overview

FrameSaver DSL Features and Benefits

Features

9783-A2-GB20-00 July

Benefits

DSL ATM

Frame Relay

FrameSaver DSL Feature Sets

Feature Set

Basic Advanced Feature

Basic Features

Maximum Number of PVCs and Management PVCs Supported

Advanced SLV Features

OpenLane SLM System

About the FrameSaver DSL Unit

User Interface Basic Operation

Procedure

Logging On

If your login was Then

Main Menu

Select

Screen Work Areas

Screen Format Description

This is a remote-site unit that supports 8 PVCs and has

Navigating the Screens

Keyboard Keys

Press

Function Keys

Select For the screen Press Enter to Function

Switching Between Screen Areas

Selecting from a Menu

Selecting a Field

Entering Information

Example

User Interface and Basic Operation

Configuration Procedures

Basic Configuration

Configuration Menu

Configuration Option Areas

Configuration Option Area Description

Accessing and Displaying Configuration Options

Main Menu → Configuration

Changing Configuration Options

Configuration → PVC Connections

Saving Configuration Options

Configuration Options

Overview

Configuration Options

Using the Easy Install Feature

Main Menu → Easy Install

Easy Install Screen Example

Easy Install Configuration Options 1

TS Access Dlci

TS Access VPI

Create a Dedicated Network Management Link

Easy Install Configuration Options 2

TS Access VCI

Ethernet Port Options Screen

Configuration → Data Ports → Dlci Records

Setting Up So the Router Can Receive RIP

Entering System Information Setting the System Clock

Main Menu → Control → System Information

Configuration Option Tables

Configuring the Overall System

System Frame Relay and LMI Options 1

Configuring Frame Relay and LMI for the System

Main Menu → Configuration → System → Frame Relay and LMI

LMI Behavior

LMI Status Enquiry N1 Possible Settings 1, 2, 3, 4

LMI Heartbeat T1 Possible Settings 5, 10, 15, 20, 25

System Frame Relay and LMI Options 2

Configuring Service Level Verification Options

Service Level Verification Options 1

Service Level Verification Options 2

SLV Timeout Clearing Event Threshold

SLV Packet Size bytes

Test Timeout

Configuring General System Options

Main Menu → Configuration → System→ General

General System Options

Main Menu → Configuration → Network → Physical

Configuring the Physical Interfaces

Configuring the Network Interface

Network Physical Interface Options

Data Port Physical Interface Options 1

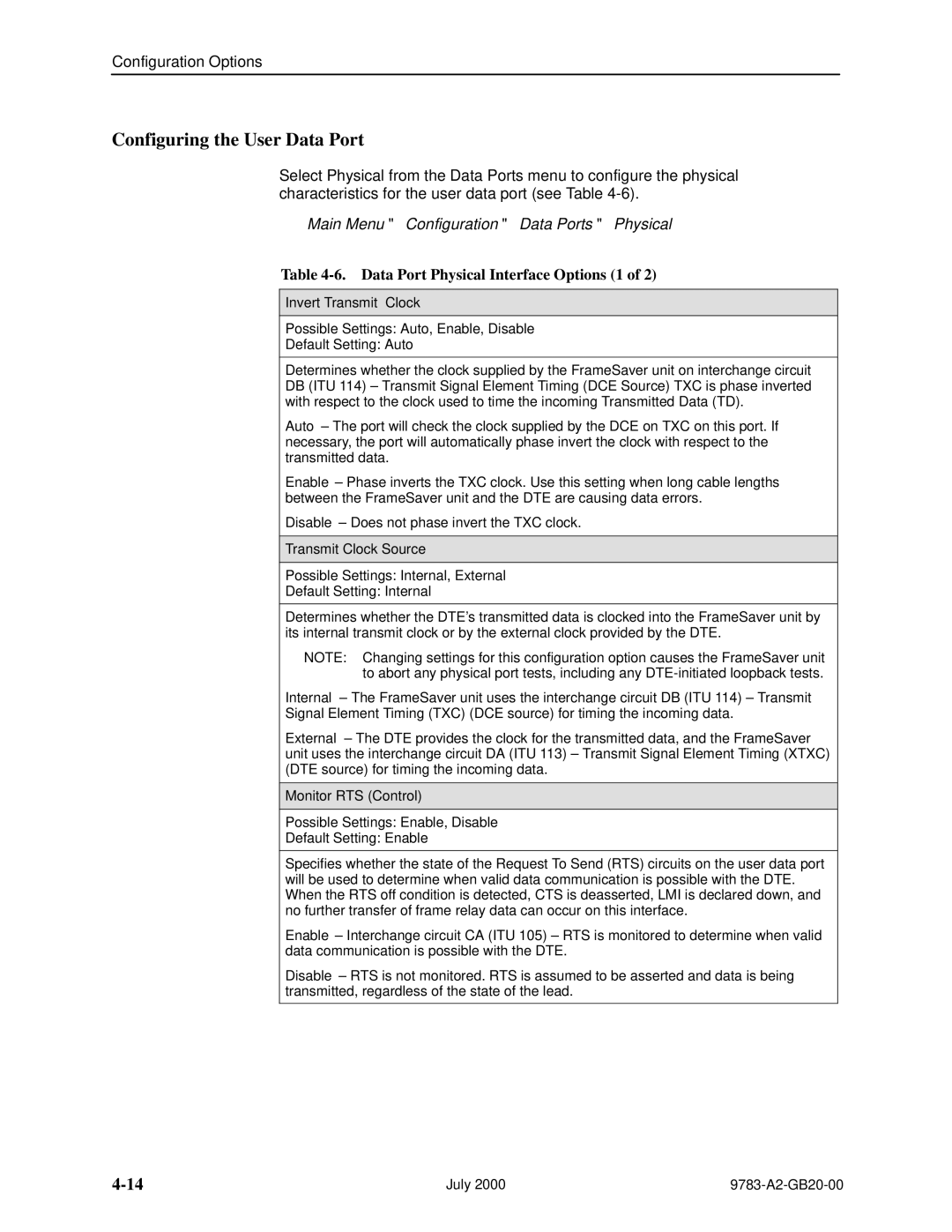

Configuring the User Data Port

Main Menu → Configuration → Data Ports → Physical

Transmit Clock Source

Data Port Physical Interface Options 2

Monitor DTR

Port DTE Initiated Loopbacks

Data Port Frame Relay Options 1

Configuring Frame Relay for the Data Port

Main Menu → Configuration → Data Ports → Frame Relay

LMI Parameters

Data Port Frame Relay Options 2

Cell Delineation Error Event Threshold

Configuring ATM for the Network Interface

Main Menu → Configuration → Network → ATM

Network ATM Options

Dlci Number

Configuring Circuit and Dlci Records

Dlci Record Options 1

VPI,VCI Number VPI

CIR bps

Dlci Type Possible Settings Standard, Multiplexed

Dlci Record Options 2

Committed Burst Size Bc Bits

Dlci Priority

Dlci Record Options 3

Excess Burst Size Bits

Outbound Management Priority

Configuring PVC Connections

Main Menu → Configuration → PVC Connections

10. PVC Connection Options 1

Destination Dlci

10. PVC Connection Options 2

Destination Link

Destination Edlci

Setting Up Management and Communication Options

Configuring Node IP Information

11. Node IP Options 1

11. Node IP Options 2

TS Access Management Link

11. Node IP Options 3

Configuring Management PVCs

12. Management PVC Options 1

Name

Primary Link Possible Settings Net1-FR1, Port-1, Clear

12. Management PVC Options 2

Set DE

12. Management PVC Options 3

Primary Dlci

Primary Edlci

13. General Snmp Management Options 1

Configuring General Snmp Management

Name 1 Access

Snmp Management

Name 2 Access

13. General Snmp Management Options 2

14. Telnet and FTP Session Options 1

Configuring Telnet and/or FTP Session Support

Telnet Login Required

Telnet Session

Inactivity Timeout

14. Telnet and FTP Session Options 2

Disconnect Time Minutes

FTP Session

FTP Login Required

14. Telnet and FTP Session Options 3

FTP Max Transfer Rate Kbps

15. Snmp NMS Security Options

Configuring Snmp NMS Security

Access Type

NMS IP Validation

Snmp Traps

Configuring Snmp Traps

16. Snmp Traps Options 1

Number of Trap Managers

16. Snmp Traps Options 2

Enterprise Specific Traps

Link Traps Interfaces

Link Traps Possible Settings Disable, Up, Down, Both

16. Snmp Traps Options 3

Rmon Traps

Configuring the Ethernet Port

17. Ethernet Port Options 1

Interface Status

17. Ethernet Port Options 2

Proxy ARP

Port Use

Configuring the Communication Port

18. Communication Port Options 1

Character Length

Stop Bits

Login Required

18. Communication Port Options 2

Ignore Control Leads

18. Communication Port Options 3

18. Communication Port Options 4

RIP

Dial-In Access

Configuring the COM Port to Support an External Modem

External Modem Commands

19. External Modem COM Port Options

Security and Logins

Limiting Access

Controlling Asynchronous Terminal Access

Set the configuration option

Controlling External COM Port Device Access

Controlling Telnet or FTP Access

Limiting Telnet Access

Limiting FTP Access

Limiting Telnet or FTP Access Over the TS Management Link

Controlling Snmp Access

Disabling Snmp Access

Assigning Snmp Community Names and Access Levels

Limiting Snmp Access Through IP Addresses

Creating a Login

Main Menu → Control → Administer Logins

Field Enter

Modifying a Login

Deleting a Login

Operation and Maintenance

Displaying System Information

Main Menu → Status → Identity

View this field To find

Viewing LEDs and Control Leads

Main Menu → Status → Display LEDs and Control Leads

Display LEDs & Control Leads Screen

LED Descriptions

General Status LEDs 1 Label Indication Color What It Means

Network Interface LEDs Label Indication Color What It Means

User Data Port LED Label Indication Color What It Means

Network Interface

Control Lead Descriptions

Additional Control Leads Label Indication What It Means

User Data Port

Device Messages

Device Messages 1 What It Indicates What To Do

Device Messages 2 What It Indicates What To Do

See Changing Software

Device Messages 3 What It Indicates What To Do

Device Messages 4 What It Indicates What To Do

See Upgrading System

Reset COM Port

Device Messages 5 What It Indicates What To Do

Status Information

Status Menu

System and Test Status Messages

Last System Reset Date and Time

Self-Test Results Messages Last System Reset Date and Time

Self-Test Results Messages

Health and Status Messages

Health and Status Messages 1 What It Indicates

Health and Status Messages 2 What It Indicates

Frame relay link

Health and Status Messages 3 What It Indicates

Frame relay link 1, 2

Test Status Messages

Test Status Messages 1 What It Indicates

Test Status Messages 2 What It Indicates

Send Pttn Active, Interface

PVC Connection Status Screen Example

PVC Connection Status

Main Menu → Status → PVC Connection Status

PVC Connection Status 1 Field

PVC Connection Status 2 Field What It Indicates

Network Interface Status Screen Example

Network Interface Status

Main Menu → Status → Network Interface Status

10. Network Interface Status Field What It Indicates

IP Routing Table

Main Menu → Status → IP Routing Table

IP Routing Table Screen Example

11. IP Routing Table Values Column What It Indicates

Performance Statistics

Main Menu → Status → Performance Statistics

Performance Statistics Menu

Performance Statistics → Frame Relay

Clearing Performance Statistics

Performance Statistics → Clear All Statistics

Performance Statistics → ESF Line

Service Level Verification Performance Statistics

Average round trip latency is measured every SLV sampling

Dlci Performance Statistics

Main Menu → Status → Performance Statistics → Dlci

13. Dlci Performance Statistics 1 What It Indicates

13. Dlci Performance Statistics 2 What It Indicates

CIR&EIR

Main Menu → Status → Performance Statistics → Frame Relay

Frame Relay Errors

Frame Relay Performance Statistics

14. Frame Relay Performance Statistics 1 What It Indicates

14. Frame Relay Performance Statistics 2 What It Indicates

Frame Relay Errors contd

Frame Relay Hdlc Errors

Frame Relay LMI

15. ATM Performance Statistics 1 What It Indicates

ATM Performance Statistics

Main Menu → Status → Performance Statistics → ATM

TC Sublayer

15. ATM Performance Statistics 2 What It Indicates

Ethernet Performance Statistics

Main Menu → Status → Performance Statistics → Ethernet

Statistic What It Indicates

Trap Event Log

Main Menu → Status → Trap Event Log

Trap Event Log Screen Example

Operation and Maintenance

FTP Operation

FTP File Transfers

Command Definition

Dir directory

Upgrading System Software

If the message displayed is Then

Determining Whether a Download Is Completed

Changing Software

Transferring Collected Data

If retrieving Then

Troubleshooting

Problem Indicators

Indicators See

Resetting the Unit and Restoring Communication

Resetting the Unit from the Control Menu

Resetting the Unit By Cycling the Power

Restoring Communication with an Improperly Configured Unit

If selecting Following occurs

Troubleshooting Management Link Feature

LMI Packet Capture Utility Feature

Main Menu → Control → LMI Packet Capture Utility

LMI Packet Capture Utility → Display LMI Trace Log

LMI Trace Log Example

Alarms

Alarm Conditions 1 What It Indicates What To Do

Alarm Conditions 2 What It Indicates What To Do

Alarm Conditions 3 What It Indicates What To Do

Alarm Conditions 4 What It Indicates What To Do

See Trap Event Log in , Operation and Maintenance

Troubleshooting Tables

Device Problems

Device Problems 1 Symptom Possible Cause Solutions

Device Problems 2 Symptom Possible Cause Solutions

Unit

ATM Problems

ATM Problems Symptom Possible Cause Solutions

Frame Relay PVC Problems

Frame Relay PVC Problems Symptom Possible Cause Solutions

Tests Available

Test Menu Example

Test Timeout Feature

When the status of a test is Only command available is

Starting and Stopping a Test

Aborting All Tests

Active

PVC Tests

PVC Tests Screen Example

Main Menu → Test → Network PVC Tests

PVC Loopback

Send Pattern

Main Menu → Test → Data Port PVC Tests

Monitor Pattern

Connectivity

DTE Loopback

Main Menu → Test → Data Port Physical Tests

IP Ping Test

Main Menu → Test → IP Ping

Procedure

Lamp Test

Main Menu → Test → Lamp Test

Setting Up OpenLane for FrameSaver Devices

OpenLane Support of FrameSaver Devices

OpenLane Support of FrameSaver Devices

Setting Up the OpenLane SLM System

Setting Up FrameSaver and SLV Support

Setting Up OpenLane for FrameSaver Devices

Setting Up Network Health for FrameSaver Devices

10-1

Installation and Setup of Network Health

Discovering FrameSaver Elements

Configuring the Discovered Elements

Grouping Elements for Reports

About Service Level Reports

Generating Reports for a Group

About At-a-Glance Reports

Reports Applicable to FrameSaver SLV Devices

About Trend Reports

Printed Reports

10-8

10-9

10-10

Menu Hierarchy

Menus

Menu Hierarchy Frame Relay Mode

Status

Easy Install

Control

Menu Hierarchy

Snmp MIBs and Traps, Rmon Alarm Defaults

MIB Support

Downloading MIBs and Snmp Traps

System Group mib-2

FrameSaver Units sysDescr system

FrameSaver Units sysObjectID system

Physical Layer

Interfaces Group mib-2

Paradyne Indexes to the Interface Table ifTable

Frame Relay Logical Layer

NetScout Indexes to the Interface Table ifTable

Rmon Logical Layer

Standards Compliance for Snmp Traps

Examples

Table B-3. warmStart Trap What It Indicates Possible Cause

Trap authenticationFailure

Trap warmStart

Variable-Binding

Traps linkUp and linkDown

Physical Sublayer

Sample strings

Table B-6. linkUp and linkDown Variable-Bindings 2

Interface Variable-Bindings Possible Cause

ATM Logical Link Sublayer

Traps enterprise-Specific

DevHealthAndStatus

SLVs devFrExt.mib

Placeholder

Traps RMON-Specific

EventIndex EventDescription EventType

Rmon Alarm and Event Defaults

Event Defaults

Rising Event Operation

Physical Interface Alarm Defaults

Frame Relay Link Alarm Defaults

Snmp MIBs and Traps, and Rmon Alarm Defaults

Dlci Alarm Defaults ± Paradyne Area

MIB FR DTE MIB

Frames Sent

Snmp MIBs and Traps, and Rmon Alarm Defaults

Object ID Cross-References Numeric Order

6.1.2.1.2.2.1

6.1.2.1.2.10.32.2.1

6.1.4.1.1795.2.24.2

6.1.4.1.1795.2.24.2.6.9.4

Dlci CIR

Dlci EIR

6.1.4.1.1795.2.24.2.6.9.4.4.2

6.1.4.1.1795.2.24.2.6.9.4.5.2.1

6.1.4.1.1795.2.24.2.6.9.4.7.1

6.1.4.1.1795.2.24.2.6.9.4.10.3.1

6.1.2.1.10.32.2.1

Snmp MIBs and Traps, and Rmon Alarm Defaults

Connectors, Cables, Pin Assignments

Rear Panel

Figure C-1. DSL Network Interface Cable with RJ48C Connector

DSL Network Interface Cable

COM Port Connector

Signal Direction Pin #

Standard EIA-232-D Crossover Cable

Pin

AT Command String To configure the modem to

Data Port Connector

Standard V.35 Straight-through Cable

Direction Pin Socket

Ethernet Port Connector

Connectors, Cables, and Pin Assignments

Technical Specifications

Ethernet Port

COM Port

DSL Network Interface

Data Port

Equipment List

Model / Feature Number

FrameSaver SLV Upgrade

Equipment

Optional Features

Description Model / Feature Number

Description Part Number Feature Number

Cables

Index

Numbers

IN-2

IN-3

IN-4

IN-5

IN-6

IN-7

IN-8

IN-9