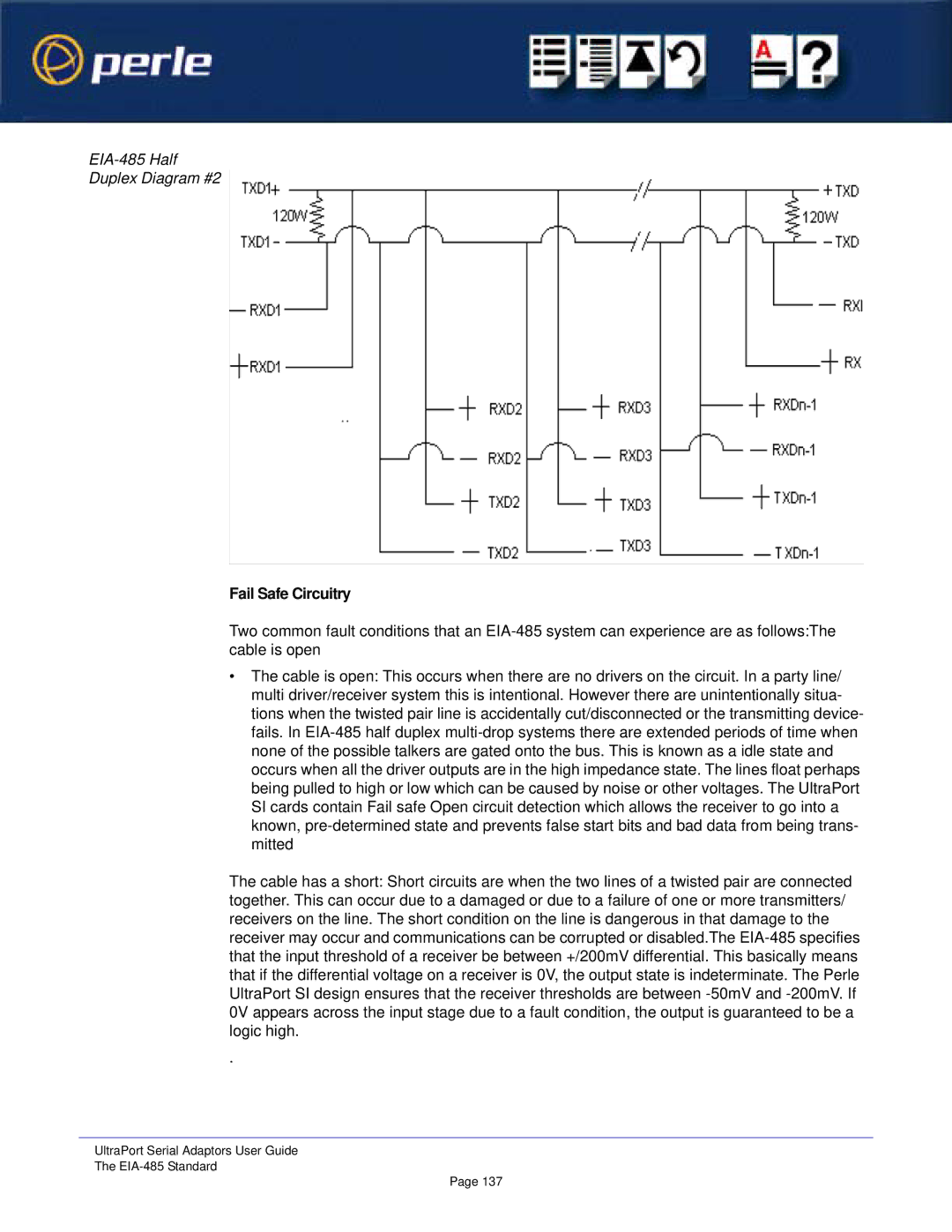

EIA-485 Half

Duplex Diagram #2

Fail Safe Circuitry

Two common fault conditions that an EIA-485 system can experience are as follows:The cable is open

•The cable is open: This occurs when there are no drivers on the circuit. In a party line/ multi driver/receiver system this is intentional. However there are unintentionally situa- tions when the twisted pair line is accidentally cut/disconnected or the transmitting device- fails. In EIA-485 half duplex multi-drop systems there are extended periods of time when none of the possible talkers are gated onto the bus. This is known as a idle state and occurs when all the driver outputs are in the high impedance state. The lines float perhaps being pulled to high or low which can be caused by noise or other voltages. The UltraPort SI cards contain Fail safe Open circuit detection which allows the receiver to go into a known, pre-determined state and prevents false start bits and bad data from being trans- mitted

The cable has a short: Short circuits are when the two lines of a twisted pair are connected together. This can occur due to a damaged or due to a failure of one or more transmitters/ receivers on the line. The short condition on the line is dangerous in that damage to the receiver may occur and communications can be corrupted or disabled.The EIA-485 specifies that the input threshold of a receiver be between +/200mV differential. This basically means that if the differential voltage on a receiver is 0V, the output state is indeterminate. The Perle UltraPort SI design ensures that the receiver thresholds are between -50mV and -200mV. If 0V appears across the input stage due to a fault condition, the output is guaranteed to be a logic high.

.

UltraPort Serial Adaptors User Guide

The EIA-485 Standard

Page 137