Programmers Guide

SPWU013A

Page

ThunderLANt Programmers Guide

Important Notice

Copyright 1996, Texas Instruments Incorporated

Read This First

Iii

Notational Conventions

If You Need Assistance

Trademarks

Contents

List Structures

Physical Interface PHY

Contentsix

Contents

Figures

Network Status Mask Register Bits

Network Configuration Register Bits

Network Status Register Bits

MAC Protocol Selection Codes

±25

Xiv

ThunderLAN Overview

ThunderLAN Architecture Networking Protocols PCI Interface

PCI

ThunderLAN Architecture

Fifo

Sram LAN

Networking Protocols

PCI Interface

PCI Cycles

Byte Ordering

Byte

Page

ThunderLAN Registers

Register Addresses

ThunderLAN Registers

PCI Configuration Space

PCI Nvram

±3. Configuration Eeprom Data Format

Word

Following example reads a byte of a PCI register

Pciint

Hostcmd Chparm Hostint Dioadr

Host Registers

Offset

+12

Host Registers

Internal Registers

HASH1 HASH2

Internal Registers

Byte

Outpwbaseaddr+OFFDIOADDR, addr

MII PHY Registers

±6. MII PHY Registers

Mdata

Possible MII interfaces Parameters Baseaddr

Delay DioRdBytebaseaddr,NetSio SetNMRST

Device to read from

#define CritOn if CritLevel == 0 \ Asm cli CritLevel++

Is the read op code for an MII management operation

Ackn bit out

Get PHY Ack Ack = inpdiodata If !ack & Mdata

Tmp = 0xffff TogLH

External Devices

Bios ROM

LEDs

Eeprom

Registers

External Devices

Eeprom

ThunderLAN Eeprom Map

Address Default Binary Bits Description

±1. ThunderLAN Eeprom Map

±1. ThunderLAN Eeprom Map

±1. ThunderLAN Eeprom Map

±1. ThunderLAN Eeprom Map

±1. ThunderLAN Eeprom Map

Initializing and Resetting

Initializing Resetting

Initializing

Finding the Network Interface Card NIC

Word PciFindDevice

Finding the Controller in Memory and I/O Space

Pciiobaselo

Finding Which Interrupt was Assigned

#define Pciintline 0x3C

Turning on the I/O Port and Memory Address Decode

Recovering the Silicon Revision Value

Setting the PCI Bus Latency Timer

Resetting

Hardware Reset

Software Reset

Page

Interrupt Handling

Loading and Unloading an Interrupt Service Routine ISR

Code that gets executed is

Nic.OldNic = HwSetIntVectorBYTEnic.Irq, NicIsr

Prioritizing Adapter Interrupts

Acknowledging Interrupts Acking

No Interrupt Invalid Code. Inttype = 000b

Interrupt Type Codes

Tx EOF Interrupt. Inttype = 001b

Rx EOF Interrupt. Inttype = 011b

Statistics Overflow Interrupt. Inttype = 010b

Dummy Interrupt. Inttype = 100b

Tx EOC Interrupt. Inttype = 101b

Network Status Interrupt. Inttype = 110b and IntVec = 00h

Adapter Check Interrupt. Inttype = 110b and IntVec ≠ 00h

±1. Adapter Check Bit Definitions

Bit Name Function

±2. Adapter Check Failure Codes

EOC/EOF

Rx EOC Interrupt. Inttype = 111b

Bit Name Channel List/Data

07h IovErr

Page

List Structures

List Management

±2. Linked List Management Technique

List Management

Cstat Field Bit Requirements

One-Fragment Mode

Receive List Format

±3. Receive List Format ± OneFrag =

±1. Receive Parameter List Fields

Field Definition

MSB LSB

±2. Receive Cstat Request Bits

Bit Name Function Ignored by adapter. Set to

EOC

±3. Receive Cstat Complete Bits

RX EOC

Transmit List Format

±7. Transmit List Format

Transmit Cstat

When nine or less fragments are used

±4. Transmit Parameter List Fields

Mand

Ignored by adapter. Should be set to

±5. Transmit Cstat Request Bits

Priority

Ing transmission requests

±6. Transmit Cstat Complete Bits

TX EOC

Frame Format GO Command

Transmitting and Receiving Frames

Frame Format

Receive Rx Frame Format

Transmit Tx Frame Format

±3. Token Ring Logical Frame Format Tx

GO Command

Starting Frame Reception Rx GO Command

GO Command

Starting Frame Transmission Tx GO Command

GO Command

GO Command

Physical Interface PHY

802.3u MII

MII-Enhanced Interrupt Event Feature

PCI Tlan

Tlan MII TNETE211

Start Operation

±1. ThunderLAN MII Pins 100M-bps CSMA/CD

Name Type Function

Register Turn Data Delimiter Code

±3. MII Frame Format Write

Name Function

Tion also disables the counter event function

±2. Possible Sources of MII Event Interrupts

Link

Mdclk Mdio

Qcyc Mint

SOF

Nonmanaged MII Devices

Bit-Rate Devices

Mcol

PHY Initialization

Page

Register Definitions

PCI Configuration Registers

Byte Device ID Vendor ID

PCI Autoconfiguration from External 24C02 Serial Eeprom

Size

PCI Vendor ID Register @ 00h Default = 104Ch

PCI Device ID Register @ 02h Default = 0500h

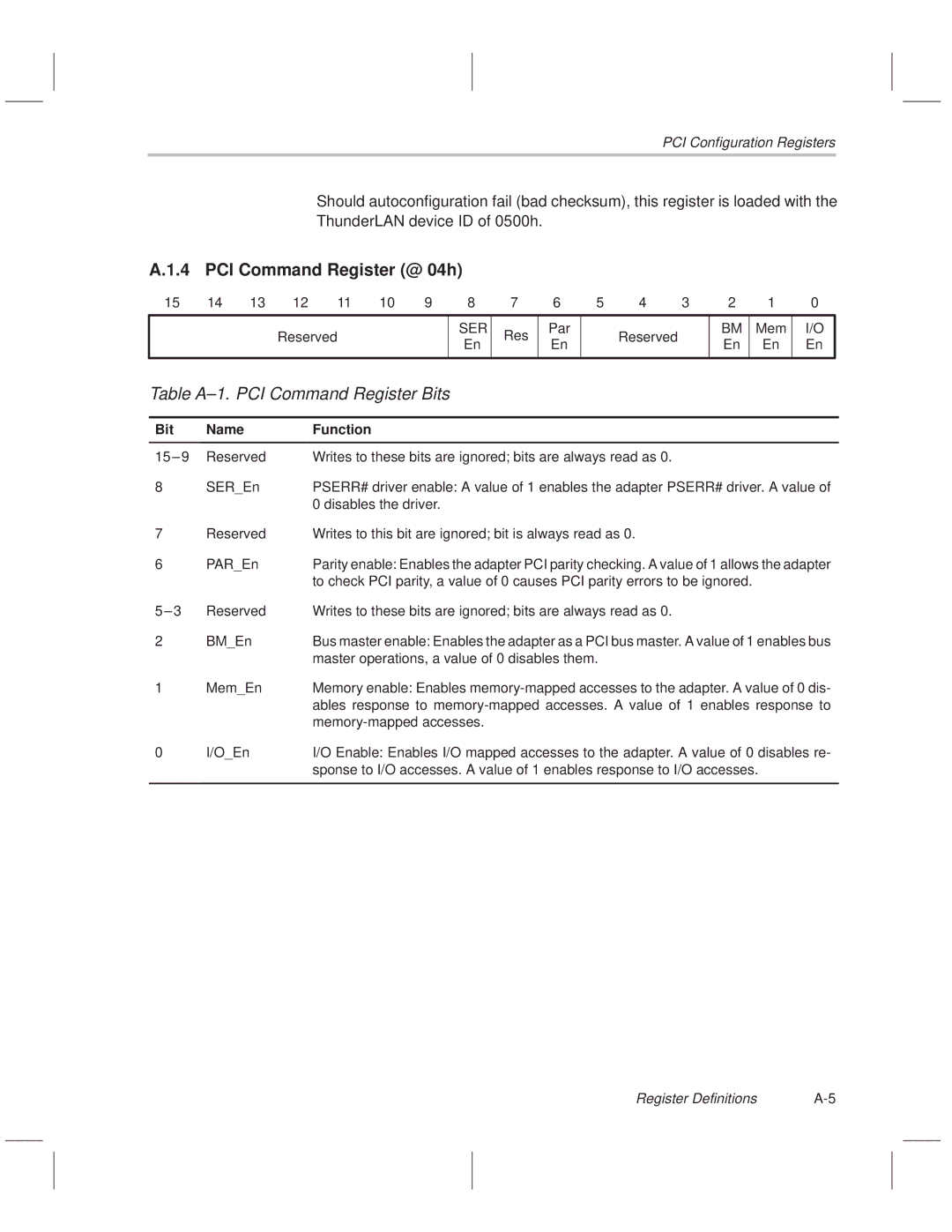

Table A±1. PCI Command Register Bits

PCI Command Register @ 04h

SER

Devsel FBB

PCI Status Register @ 06h

Table A±2. PCI Status Register Bits

PDEVSEL#

PCI Subclass Register @ 0Ah

PCI Latency Timer Register @ 0Dh

PCI Base Class Register @ 0Bh

PCI Program Interface Register @ 09h

PCI Nvram Register @ 34h

PCI Bios ROM Base Address Register @ 30h

PCI Memory Base Address Register @ 14h

Memory Base Address 12 LSBs Memory Base Address 16 MSBs

PCI Interrupt Line Register @ 3Ch

Table A±3. PCI Nvram Register Bits

PCI Interrupt Pin Register @ 3Dh

PCI MinGnt @ 3Eh and MaxLat @ 3Fh Registers

PCI Reset Control Register @ 40h

Table A±4. PCI Reset Control Register Bits

Srdis

CardBus CIS Pointer @ 28h

Table A±5. HostCMD Register Bits

Host Command Register±HOSTCMD @ BaseAddress + 0 Host

Adapter Host Registers

Hostcmd

Table A±5. HostCMD Register Bits

If Nes = 1, EOC = 0, and R/T = 0 Tx EOF Ack

Cated in ChSel

If Nes = 1, EOC = 1, and R/T = 1 Rx EOC Ack

Raised

To be issued in a single write cycle Nes

Lected otherwise statistics commands are selected

Be issued in a single write cycle

Lected. If set to a 0, EOF operations are selected

ChSel must indicate the selected transmit channel

LdTmr

LdThr

ReqInt

Channel Parameter Register±CHPARM @ BaseAddress + 4 Host

Host Interrupt Register±HOSTINT @ BaseAddress + 10 Host

Table A±6. Hostint Register Bits

DIO Address Register±DIOADR @ BaseAddress + 8 Host

Table A±7. Dioadr Register Bits

DIO Data Register±DIODATA @ BaseAddress + 12 Host

Adapter Internal Registers

Tx underrun

ManTest NetConfig

HASH2 HASH1

Late

Network Command Register±NetCmd @ 0x00 DIO

Table A±8. Network Command Register Bits

Network Serial I/O Register±NetSio @ 0x00 DIO

Table A±9. Network Serial I/O Register Bits

Network Status Register±NetSts @ 0x00 DIO

Table A±10. Network Status Register Bits

Network Status Mask Register±NetMask @ 0x00 DIO

Table A±11. Network Status Mask Register Bits

Table A±12. Network Configuration Register Bits

Network Configuration Register±NetConfig @ 0x04 DIO

BIT PEF

Mtest

Manufacturing Test Register±ManTest @ 0x04 DIO

Default PCI Parameter Registers±@ 0x08±0x0C DIO

Table A±13. MAC Protocol Selection Codes

Code MAC Protocol Selected

General Address Registers±Areg0-3 @ 0x10±0x24 DIO

All-Nodes Broadcast Address

Hash Address Registers±HASH1/HASH2 @ 0x28±0x2C DIO

Good Tx frames 0x34 Rx overrun

Network Statistics Registers±@ 0x30±0x40 DIO

0x3C Single collision Tx frames

Table A±14. Ethernet Error Counters

Counter Definition

Table A±15. Demand Priority Error Counters

Adapter Commit Register±Acommit @ 0x40 DIO Byte

31±28 Tx commit

Table A±16. Adapter Commit Register Bits

LED Register±LEDreg @ 0x44 DIO Byte

Level

Burst Size Register±BSIZEreg @ 0x44 DIO Byte

Table A±17. Burst Size Register Bits

Maximum Rx Frame Size Register±MaxRx @ 0x44 DIO Bytes 2+3

Byte Maximum Rx frame size in units of 8 bits

Disabled. Default value is

Interrupt Disable Register Intdis @ 0x48 DIO Byte

Table A±18. Demand Priority Error Counters

RX EOF

10Base-T PHY Registers

Figure A±8 Base-T PHY Registers

PHY Generic Control Register±GENctl @

Table A±19. PHY Generic Control Register Bits

Coltest

Nal Mcol whenever the transmit enable Mtxen pin is asserted

Fect on PHY operation

Reserved Read as

Autocomplt Rflt Link Jabber

PHY Generic Status Register±GENsts @

Table A±20. PHY Generic Status Register Bits

Autocmplt

Jabber

PHY Generic Identifier±GENidhi/GENidlo @ 0x2/0x3

OUI Manufacturers model number Revision number

Table A±21. Autonegotiation Advertisement Register Bits

Autonegotiation Advertisement Register±ANadv @

Tlrflt

Lpnxtpage

Autonegotiation Link Partner Ability Register±ANlpa @

Lprflt

Pardetflt Lpnpable Pagerx Lpanable

Autonegotiation Expansion Register±ANexp @

Table A±23. Autonegotiation Expansion Register Bits

Pardetflt

ThunderLAN PHY Identifier High/Low±TLPHYid @

ThunderLAN PHY Control Register±TLPHYctl @

Table A±24. ThunderLAN PHY Control Register Bits

Inten

ThunderLAN PHY Status Register±TLPHYsts @

Table A±25. ThunderLAN PHY Status Register Bits

Mint Phok Polok

Tpenergy

POLOK²

Inverted link pulses has been detected

Set.²

Page

PMI Interface

100VG-AnyLAN Training TNETE211 Register Descriptions

100VG-AnyLAN Training

Figure B±1 .12 Training Frame Format

100VG-AnyLAN Training

Figure B±2. Training Flowchart

100VG-AnyLAN Training

TNETE211 Register Descriptions

Table B±1. PHY Generic Control Register Bits

Reset Loopbk Pdown Isolate

Autoconfiguration enable Not implemented

0x01 PHY generic status register 0x02

Table B±2. PHY Generic Status Register Bits

PHY Generic Status Register ±GENsts @

Rflt Link Jabber

Iglink Mcrs Ptlswen Prlsren

Trfail Tridle Npmdw Nfew Inten Tint

Table B±3. ThunderLAN PHY Control Register Bits

Retrain

Mint Phok Config Retrain Lstate Trfrto Rtridl Lrcv Lsil

Table B±4. ThunderLAN PHY Status Register Bits

Lstate

Rtridl

Trfrto

Inten bit is also set, this causes an MII interrupt

Lrcv

TNETE100PM/TNETE110PM