|

|

|

| CY7C65113C |

|

|

|

|

|

|

|

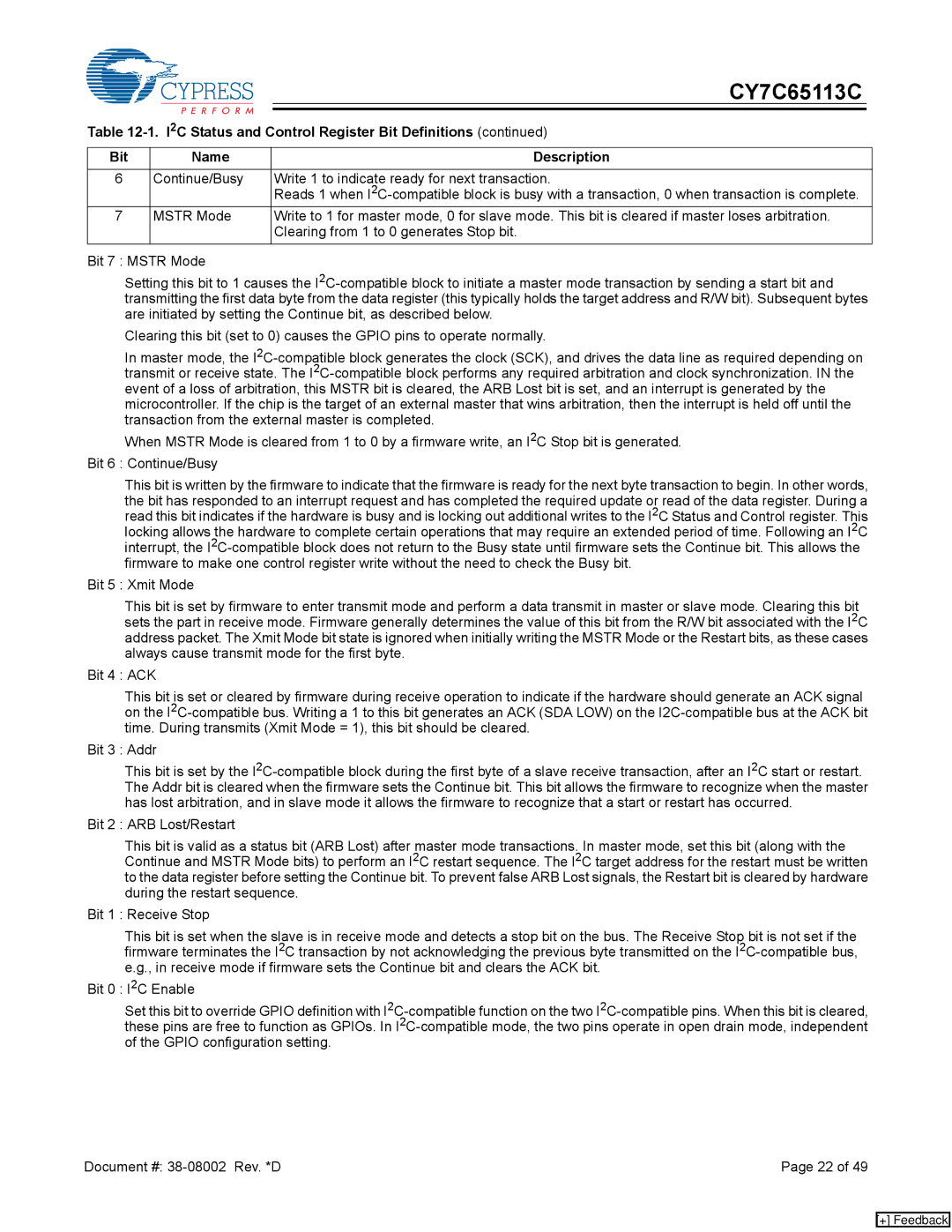

Table |

| ||||

Bit |

| Name |

| Description |

|

|

|

|

|

| |

6 | Continue/Busy |

| Write 1 to indicate ready for next transaction. |

| |

|

|

|

| Reads 1 when |

|

7 | MSTR Mode |

| Write to 1 for master mode, 0 for slave mode. This bit is cleared if master loses arbitration. |

| |

|

|

|

| Clearing from 1 to 0 generates Stop bit. |

|

Bit 7 : MSTR Mode

Setting this bit to 1 causes the

Clearing this bit (set to 0) causes the GPIO pins to operate normally.

In master mode, the

When MSTR Mode is cleared from 1 to 0 by a firmware write, an I2C Stop bit is generated. Bit 6 : Continue/Busy

This bit is written by the firmware to indicate that the firmware is ready for the next byte transaction to begin. In other words, the bit has responded to an interrupt request and has completed the required update or read of the data register. During a read this bit indicates if the hardware is busy and is locking out additional writes to the I2C Status and Control register. This locking allows the hardware to complete certain operations that may require an extended period of time. Following an I2C interrupt, the

Bit 5 : Xmit Mode

This bit is set by firmware to enter transmit mode and perform a data transmit in master or slave mode. Clearing this bit sets the part in receive mode. Firmware generally determines the value of this bit from the R/W bit associated with the I2C address packet. The Xmit Mode bit state is ignored when initially writing the MSTR Mode or the Restart bits, as these cases always cause transmit mode for the first byte.

Bit 4 : ACK

This bit is set or cleared by firmware during receive operation to indicate if the hardware should generate an ACK signal on the

Bit 3 : Addr

This bit is set by the

Bit 2 : ARB Lost/Restart

This bit is valid as a status bit (ARB Lost) after master mode transactions. In master mode, set this bit (along with the Continue and MSTR Mode bits) to perform an I2C restart sequence. The I2C target address for the restart must be written to the data register before setting the Continue bit. To prevent false ARB Lost signals, the Restart bit is cleared by hardware during the restart sequence.

Bit 1 : Receive Stop

This bit is set when the slave is in receive mode and detects a stop bit on the bus. The Receive Stop bit is not set if the firmware terminates the I2C transaction by not acknowledging the previous byte transmitted on the

Bit 0 : I2C Enable

Set this bit to override GPIO definition with

Document #: | Page 22 of 49 |

[+] Feedback