CY7C65113C

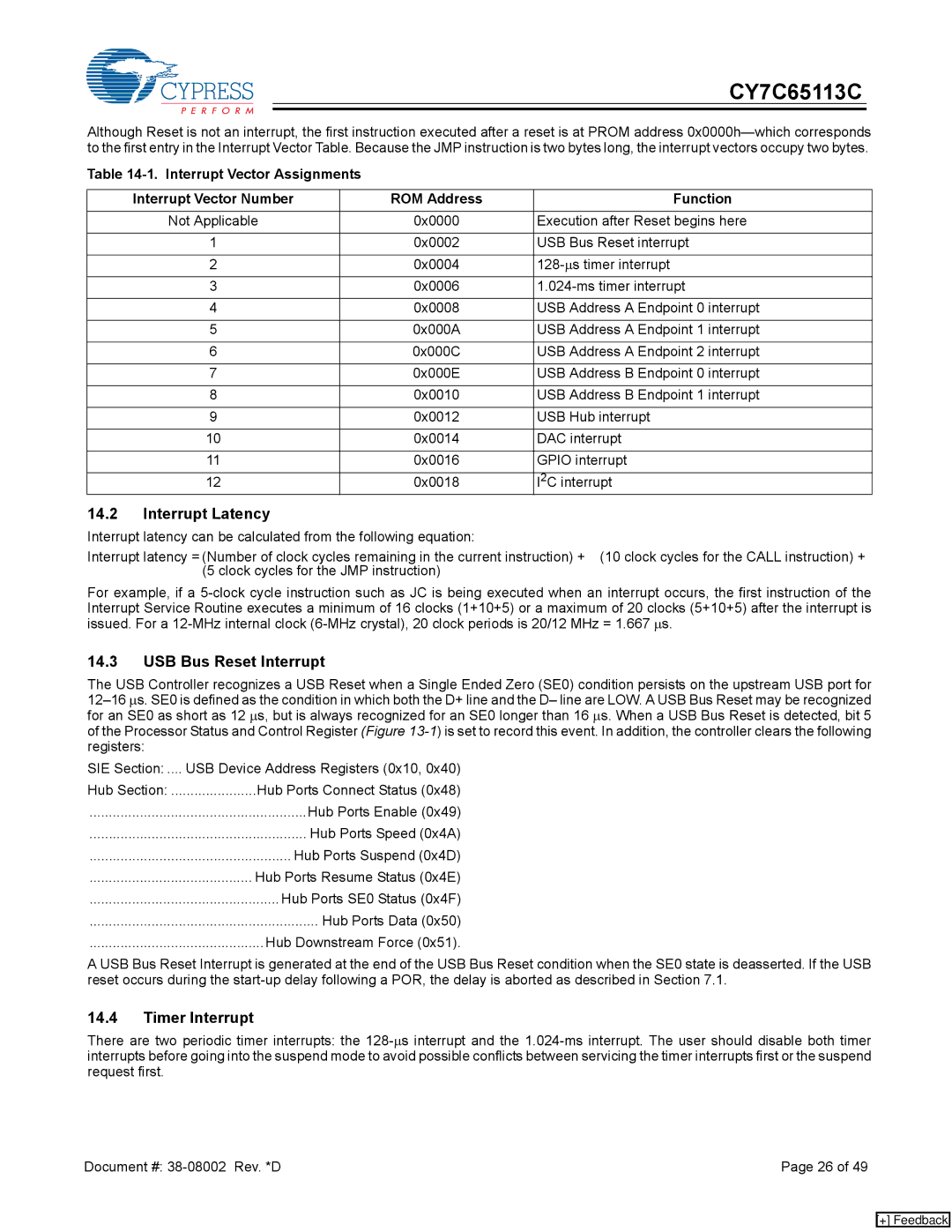

Although Reset is not an interrupt, the first instruction executed after a reset is at PROM address

Table

Interrupt Vector Number | ROM Address | Function |

Not Applicable | 0x0000 | Execution after Reset begins here |

|

|

|

1 | 0x0002 | USB Bus Reset interrupt |

|

|

|

2 | 0x0004 | |

|

|

|

3 | 0x0006 | |

|

|

|

4 | 0x0008 | USB Address A Endpoint 0 interrupt |

|

|

|

5 | 0x000A | USB Address A Endpoint 1 interrupt |

|

|

|

6 | 0x000C | USB Address A Endpoint 2 interrupt |

|

|

|

7 | 0x000E | USB Address B Endpoint 0 interrupt |

|

|

|

8 | 0x0010 | USB Address B Endpoint 1 interrupt |

|

|

|

9 | 0x0012 | USB Hub interrupt |

|

|

|

10 | 0x0014 | DAC interrupt |

|

|

|

11 | 0x0016 | GPIO interrupt |

|

|

|

12 | 0x0018 | I2C interrupt |

14.2Interrupt Latency

Interrupt latency can be calculated from the following equation:

Interrupt latency = (Number of clock cycles remaining in the current instruction) + (10 clock cycles for the CALL instruction) + (5 clock cycles for the JMP instruction)

For example, if a

14.3USB Bus Reset Interrupt

The USB Controller recognizes a USB Reset when a Single Ended Zero (SE0) condition persists on the upstream USB port for

SIE Section: .... | USB Device Address Registers (0x10, 0x40) |

Hub Section: | Hub Ports Connect Status (0x48) |

........................................................ | Hub Ports Enable (0x49) |

........................................................ | Hub Ports Speed (0x4A) |

.................................................... | Hub Ports Suspend (0x4D) |

.......................................... | Hub Ports Resume Status (0x4E) |

................................................. | Hub Ports SE0 Status (0x4F) |

........................................................... | Hub Ports Data (0x50) |

............................................. | Hub Downstream Force (0x51). |

A USB Bus Reset Interrupt is generated at the end of the USB Bus Reset condition when the SE0 state is deasserted. If the USB reset occurs during the

14.4Timer Interrupt

There are two periodic timer interrupts: the

Document #: | Page 26 of 49 |

[+] Feedback