CY7C65113C

7.2Watchdog Reset

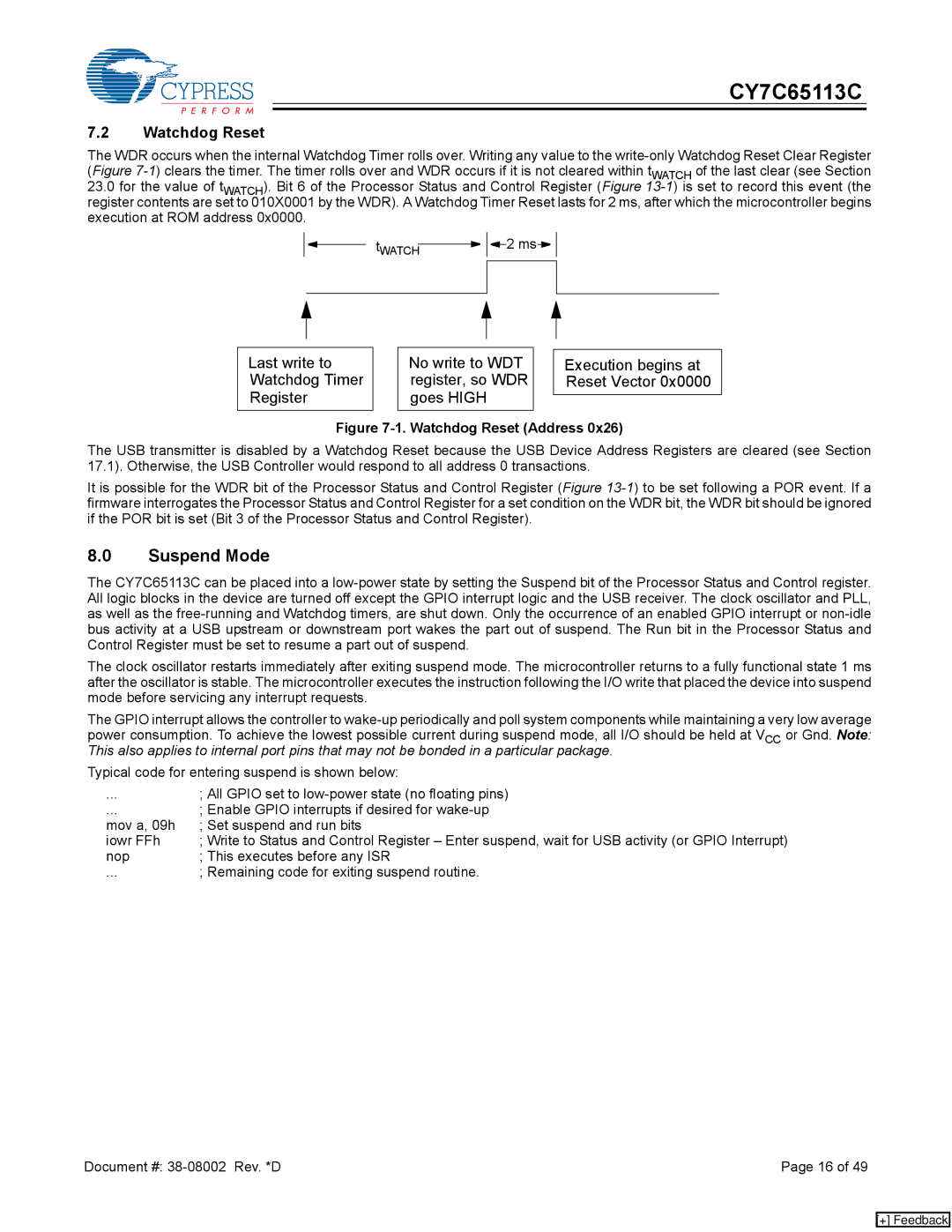

The WDR occurs when the internal Watchdog Timer rolls over. Writing any value to the

tWATCH![]()

![]()

![]()

![]() 2 ms

2 ms![]()

![]()

![]()

Last write to Watchdog Timer Register

No write to WDT register, so WDR goes HIGH

Execution begins at Reset Vector 0x0000

Figure 7-1. Watchdog Reset (Address 0x26)

The USB transmitter is disabled by a Watchdog Reset because the USB Device Address Registers are cleared (see Section 17.1). Otherwise, the USB Controller would respond to all address 0 transactions.

It is possible for the WDR bit of the Processor Status and Control Register (Figure

8.0Suspend Mode

The CY7C65113C can be placed into a

The clock oscillator restarts immediately after exiting suspend mode. The microcontroller returns to a fully functional state 1 ms after the oscillator is stable. The microcontroller executes the instruction following the I/O write that placed the device into suspend mode before servicing any interrupt requests.

The GPIO interrupt allows the controller to

Typical code for entering suspend is shown below:

... | ; All GPIO set to |

... | ; Enable GPIO interrupts if desired for |

mov a, 09h | ; Set suspend and run bits |

iowr FFh | ; Write to Status and Control Register – Enter suspend, wait for USB activity (or GPIO Interrupt) |

nop | ; This executes before any ISR |

... | ; Remaining code for exiting suspend routine. |

Document #: | Page 16 of 49 |

[+] Feedback