CY7C65113C

5.28-bit Accumulator (A)

The accumulator is the

5.38-bit Temporary Register (X)

The “X” register is available to the firmware for temporary storage of intermediate results. The microcontroller can perform indexed operations based on the value in X. Refer to Section 5.6.3 for additional information.

5.48-bit Program Stack Pointer (PSP)

During a reset, the Program Stack Pointer (PSP) is set to 0x00 and “grows” upward from this address. The PSP may be set by firmware, using the MOV PSP,A instruction. The PSP supports interrupt service under hardware control and CALL, RET, and RETI instructions under firmware control. The PSP is not readable by the firmware.

During an interrupt acknowledge, interrupts are disabled and the

The Return From Interrupt (RETI) instruction decrements the PSP, then restores the second byte from memory addressed by the PSP. The PSP is decremented again and the first byte is restored from memory addressed by the PSP. After the program counter and flags have been restored from stack, the interrupts are enabled. The overall effect is to restore the program counter and flags from the program stack, decrement the PSP by two, and

The Call Subroutine (CALL) instruction stores the program counter and flags on the program stack and increments the PSP by two.

The Return From Subroutine (RET) instruction restores the program counter but not the flags from the program stack and decrements the PSP by two.

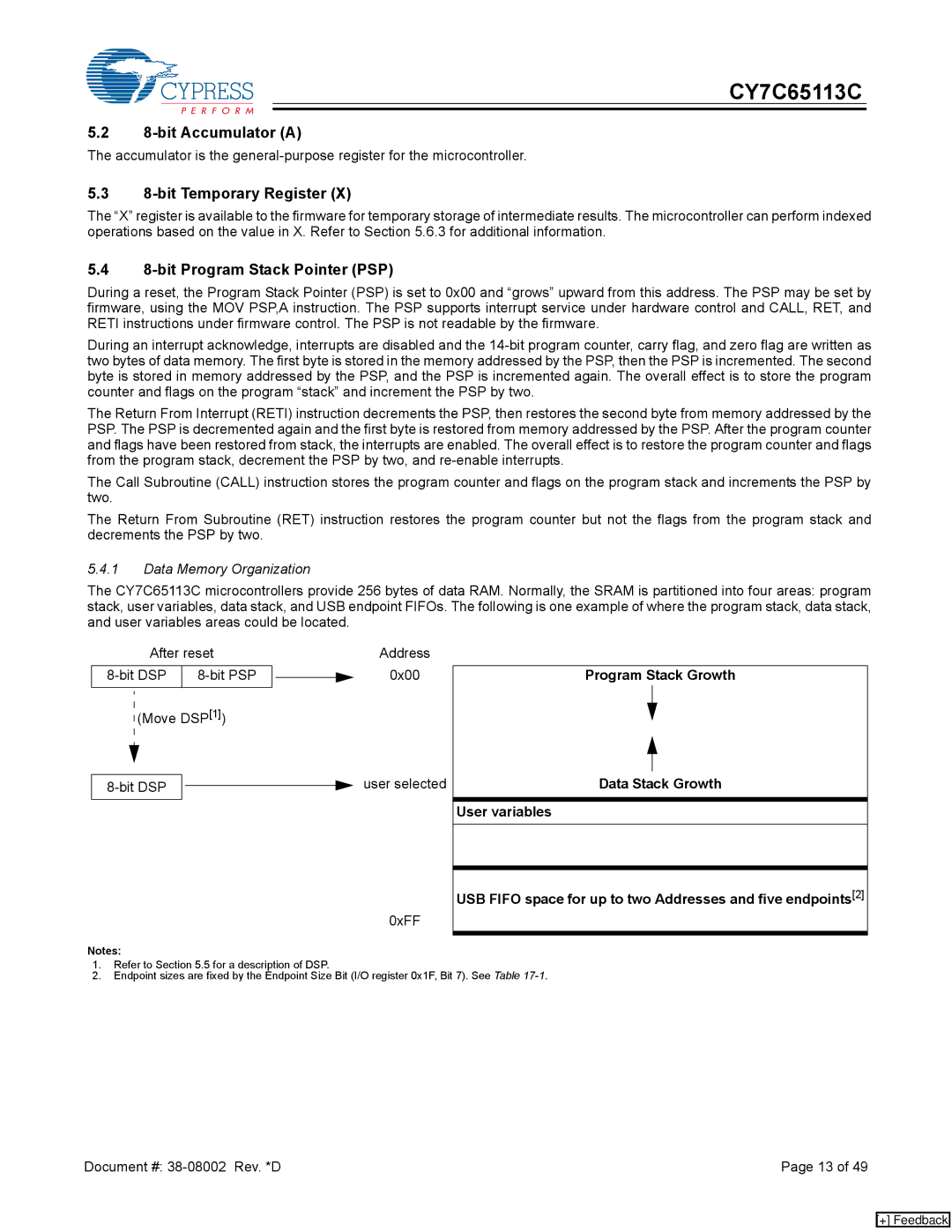

5.4.1Data Memory Organization

The CY7C65113C microcontrollers provide 256 bytes of data RAM. Normally, the SRAM is partitioned into four areas: program stack, user variables, data stack, and USB endpoint FIFOs. The following is one example of where the program stack, data stack, and user variables areas could be located.

After reset

|

|

(Move DSP[1])

Address

0x00

user selected

0xFF

Program Stack Growth

Data Stack Growth

User variables

USB FIFO space for up to two Addresses and five endpoints[2]

Notes:

1.Refer to Section 5.5 for a description of DSP.

2.Endpoint sizes are fixed by the Endpoint Size Bit (I/O register 0x1F, Bit 7). See Table

Document #: | Page 13 of 49 |

[+] Feedback