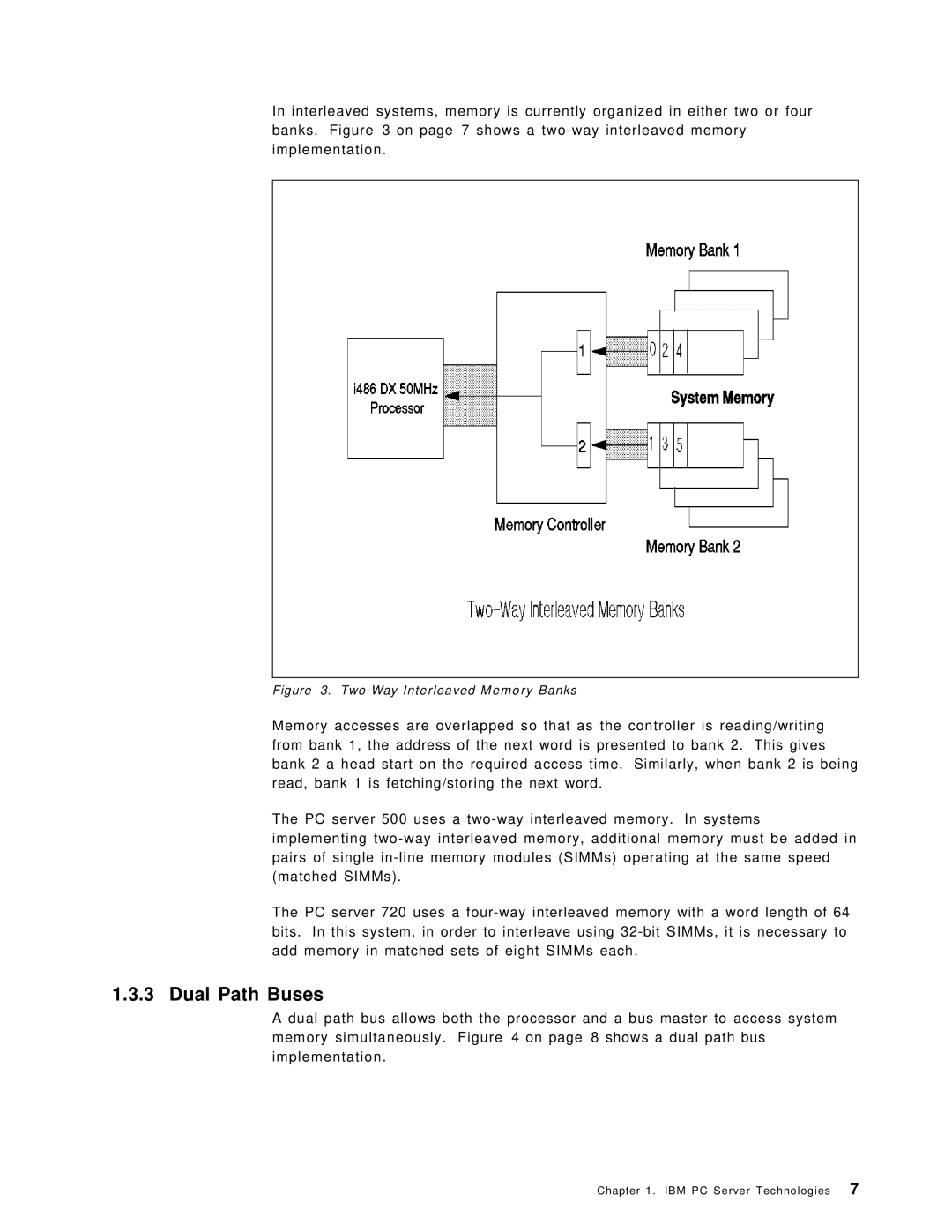

In interleaved systems, memory is currently organized in either two or four banks. Figure 3 on page 7 shows a

Figure 3. Two-Way Interleaved Memory Banks

Memory accesses are overlapped so that as the controller is reading/writing from bank 1, the address of the next word is presented to bank 2. This gives bank 2 a head start on the required access time. Similarly, when bank 2 is being read, bank 1 is fetching/storing the next word.

The PC server 500 uses a

The PC server 720 uses a

1.3.3 Dual Path Buses

A dual path bus allows both the processor and a bus master to access system memory simultaneously. Figure 4 on page 8 shows a dual path bus implementation.

Chapter 1. IBM PC Server Technologies 7