PCI-X Layout Guidelines

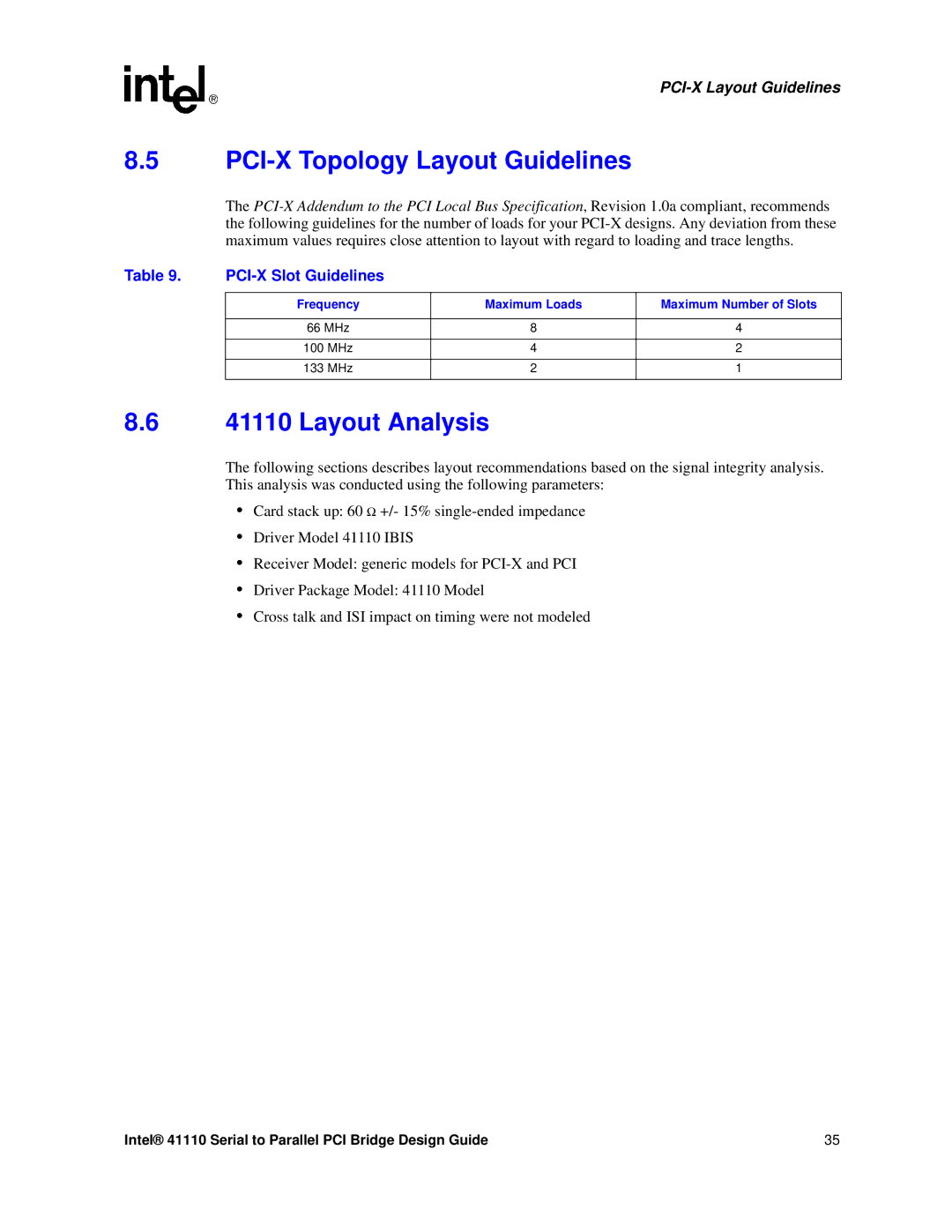

8.5PCI-X Topology Layout Guidelines

The

Table 9. |

|

|

|

|

|

|

|

| Frequency | Maximum Loads | Maximum Number of Slots |

|

|

|

|

| 66 MHz | 8 | 4 |

|

|

|

|

| 100 MHz | 4 | 2 |

|

|

|

|

| 133 MHz | 2 | 1 |

|

|

|

|

8.641110 Layout Analysis

The following sections describes layout recommendations based on the signal integrity analysis. This analysis was conducted using the following parameters:

•Card stack up: 60 Ω +/- 15%

•Driver Model 41110 IBIS

•Receiver Model: generic models for

•Driver Package Model: 41110 Model

•Cross talk and ISI impact on timing were not modeled

Intel® 41110 Serial to Parallel PCI Bridge Design Guide | 35 |