PCI-X Layout Guidelines

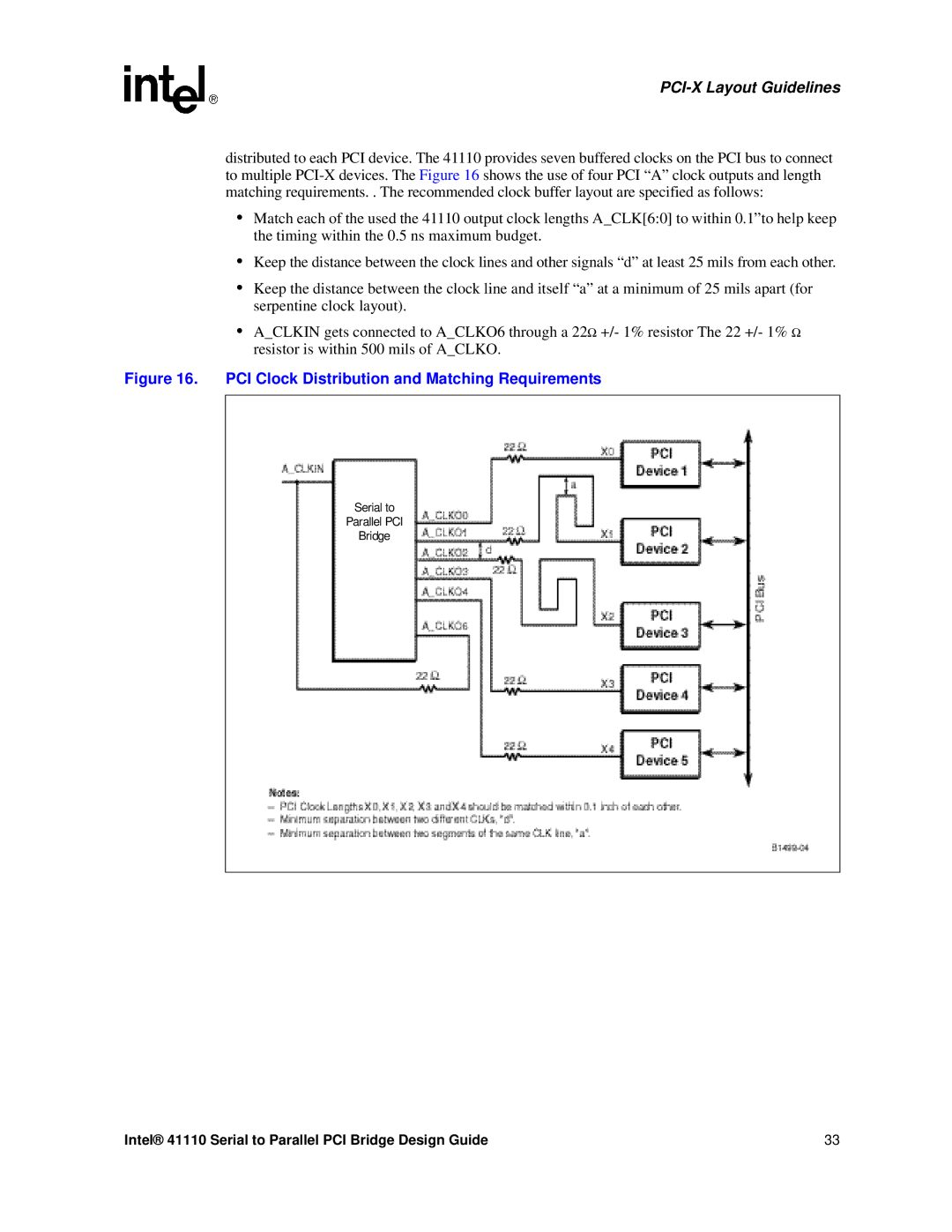

distributed to each PCI device. The 41110 provides seven buffered clocks on the PCI bus to connect to multiple

•Match each of the used the 41110 output clock lengths A_CLK[6:0] to within 0.1”to help keep the timing within the 0.5 ns maximum budget.

•Keep the distance between the clock lines and other signals “d” at least 25 mils from each other.

•Keep the distance between the clock line and itself “a” at a minimum of 25 mils apart (for serpentine clock layout).

•A_CLKIN gets connected to A_CLKO6 through a 22Ω +/- 1% resistor The 22 +/- 1% Ω resistor is within 500 mils of A_CLKO.

Figure 16. PCI Clock Distribution and Matching Requirements

Serial to

Parallel PCI

Bridge

Intel® 41110 Serial to Parallel PCI Bridge Design Guide | 33 |