Intel® IQ80321 I/O Processor Evaluation Platform

Hardware Reference Section

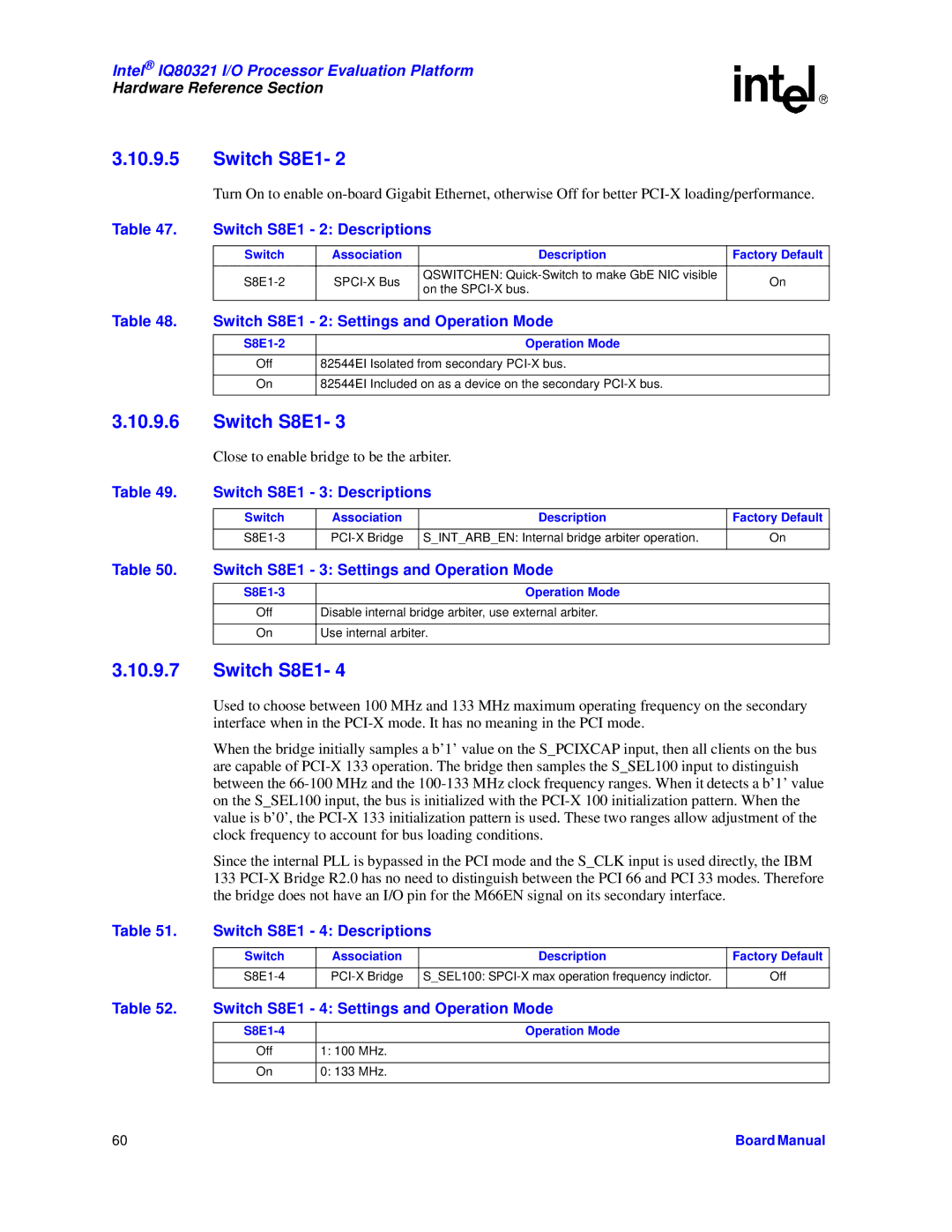

3.10.9.5Switch S8E1- 2

Turn On to enable

Table 47. | Switch S8E1 - 2: Descriptions |

| ||

|

|

|

|

|

| Switch | Association | Description | Factory Default |

|

|

|

|

|

| QSWITCHEN: | On | ||

| on the | |||

|

|

|

| |

|

|

|

|

|

Table 48. | Switch S8E1 - 2: Settings and Operation Mode | |

|

| Operation Mode |

|

|

|

| Off | 82544EI Isolated from secondary |

|

|

|

| On | 82544EI Included on as a device on the secondary |

|

|

|

3.10.9.6Switch S8E1- 3

Close to enable bridge to be the arbiter.

Table 49. | Switch S8E1 - 3: Descriptions |

| ||

|

|

|

|

|

| Switch | Association | Description | Factory Default |

|

|

|

|

|

| S_INT_ARB_EN: Internal bridge arbiter operation. | On | ||

|

|

|

|

|

Table 50. | Switch S8E1 - 3: Settings and Operation Mode |

| ||

|

|

|

|

|

|

| Operation Mode |

| |

|

|

|

| |

| Off | Disable internal bridge arbiter, use external arbiter. |

| |

|

|

|

| |

| On | Use internal arbiter. |

| |

|

|

|

|

|

3.10.9.7Switch S8E1- 4

Used to choose between 100 MHz and 133 MHz maximum operating frequency on the secondary interface when in the

When the bridge initially samples a b’1’ value on the S_PCIXCAP input, then all clients on the bus are capable of

Since the internal PLL is bypassed in the PCI mode and the S_CLK input is used directly, the IBM 133

Table 51. | Switch S8E1 - 4: Descriptions |

| ||

|

|

|

|

|

| Switch | Association | Description | Factory Default |

|

|

|

|

|

| S_SEL100: | Off | ||

|

|

|

|

|

Table 52. | Switch S8E1 - 4: Settings and Operation Mode |

| ||

|

|

|

|

|

|

| Operation Mode |

| |

|

|

|

|

|

| Off | 1: 100 MHz. |

|

|

|

|

|

|

|

| On | 0: 133 MHz. |

|

|

|

|

|

|

|

60 | Board Manual |