| Intel® IQ80321 I/O Processor Evaluation Platform | |

|

| Contents |

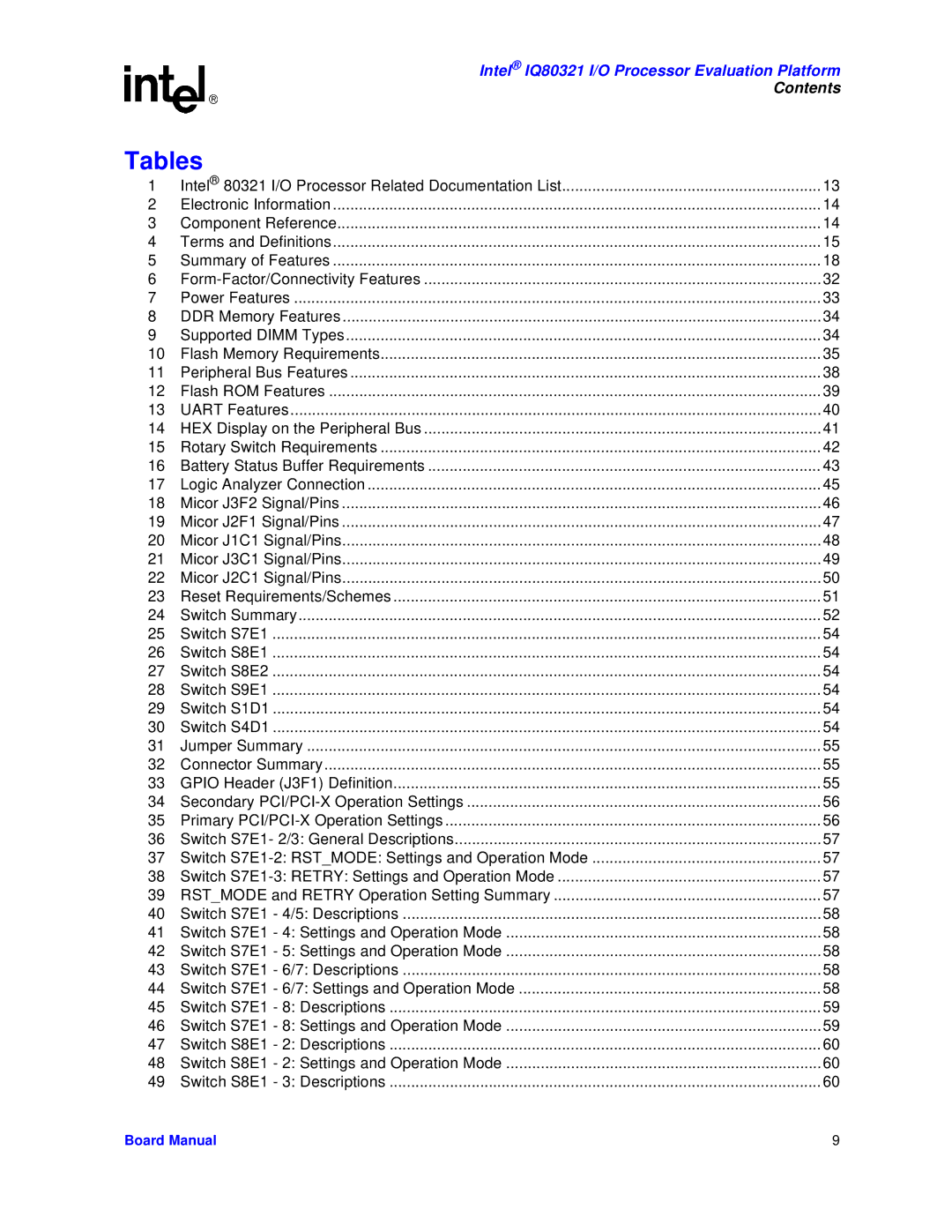

Tables |

| |

1 | Intel® 80321 I/O Processor Related Documentation List | 13 |

2 | Electronic Information | 14 |

3 | Component Reference | 14 |

4 | Terms and Definitions | 15 |

5 | Summary of Features | 18 |

6 | 32 | |

7 | Power Features | 33 |

8 | DDR Memory Features | 34 |

9 | Supported DIMM Types | 34 |

10 | Flash Memory Requirements | 35 |

11 | Peripheral Bus Features | 38 |

12 | Flash ROM Features | 39 |

13 | UART Features | 40 |

14 | HEX Display on the Peripheral Bus | 41 |

15 | Rotary Switch Requirements | 42 |

16 | Battery Status Buffer Requirements | 43 |

17 | Logic Analyzer Connection | 45 |

18 | Micor J3F2 Signal/Pins | 46 |

19 | Micor J2F1 Signal/Pins | 47 |

20 | Micor J1C1 Signal/Pins | 48 |

21 | Micor J3C1 Signal/Pins | 49 |

22 | Micor J2C1 Signal/Pins | 50 |

23 | Reset Requirements/Schemes | 51 |

24 | Switch Summary | 52 |

25 | Switch S7E1 | 54 |

26 | Switch S8E1 | 54 |

27 | Switch S8E2 | 54 |

28 | Switch S9E1 | 54 |

29 | Switch S1D1 | 54 |

30 | Switch S4D1 | 54 |

31 | Jumper Summary | 55 |

32 | Connector Summary | 55 |

33 | GPIO Header (J3F1) Definition | 55 |

34 | Secondary | 56 |

35 | Primary | 56 |

36 | Switch S7E1- 2/3: General Descriptions | 57 |

37 | Switch | 57 |

38 | Switch | 57 |

39 | RST_MODE and RETRY Operation Setting Summary | 57 |

40 | Switch S7E1 - 4/5: Descriptions | 58 |

41 | Switch S7E1 - 4: Settings and Operation Mode | 58 |

42 | Switch S7E1 - 5: Settings and Operation Mode | 58 |

43 | Switch S7E1 - 6/7: Descriptions | 58 |

44 | Switch S7E1 - 6/7: Settings and Operation Mode | 58 |

45 | Switch S7E1 - 8: Descriptions | 59 |

46 | Switch S7E1 - 8: Settings and Operation Mode | 59 |

47 | Switch S8E1 - 2: Descriptions | 60 |

48 | Switch S8E1 - 2: Settings and Operation Mode | 60 |

49 | Switch S8E1 - 3: Descriptions | 60 |

Board Manual | 9 |