Software Reference | 5 |

5.1DRAM

For DDR SDRAM Sizes and Configurations, see section 7.2.2.1, table 139 of theIntel® 80321 I/O Processor Developer’s Manual. Table 89 provides DDR SDRAM Address Register Definitions, while this sections also contains multiple examples of Address Register Programming.

See the Intel® 80321 I/O Processor Design Guide, section 7.1, table 16 for supported DDR and SDRAM configurations.

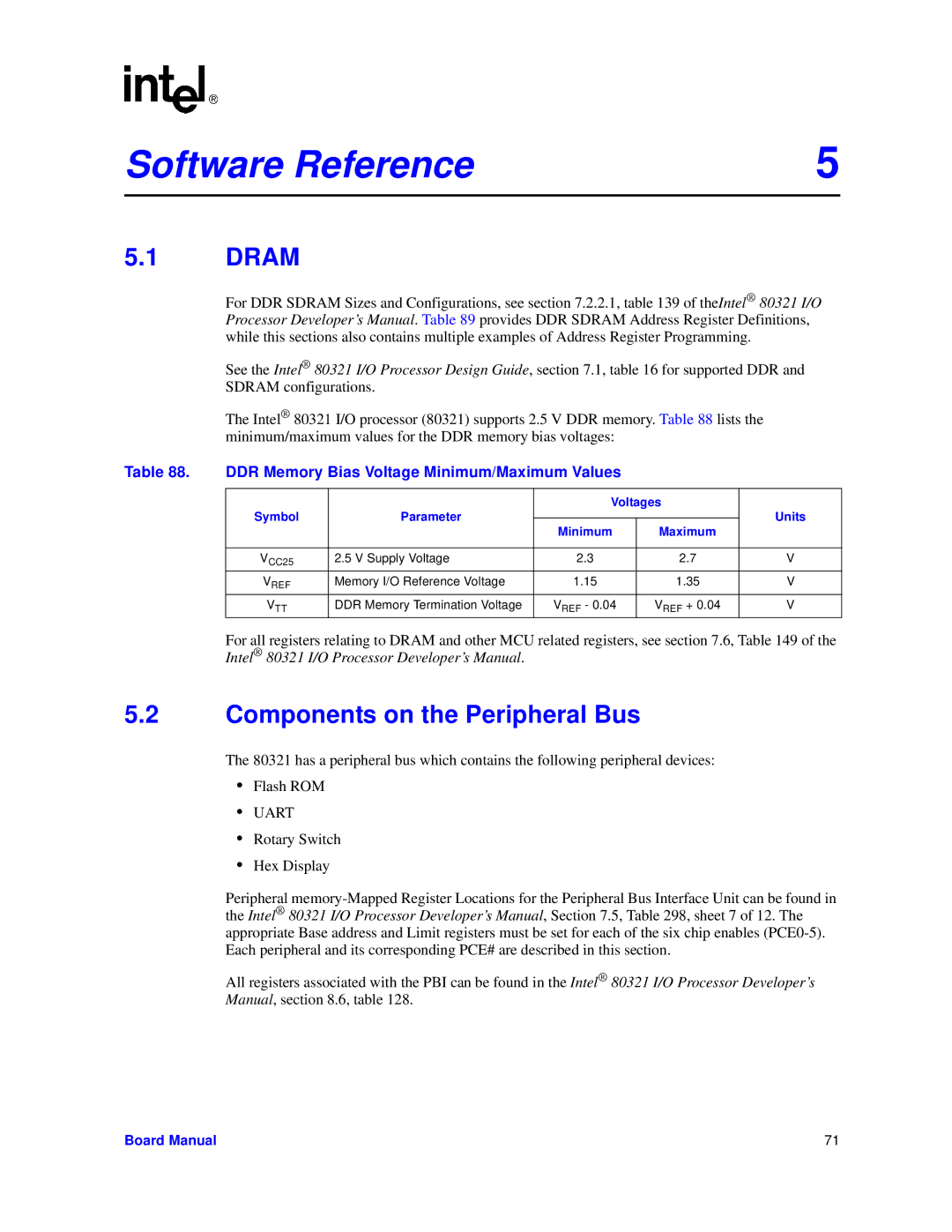

The Intel® 80321 I/O processor (80321) supports 2.5 V DDR memory. Table 88 lists the minimum/maximum values for the DDR memory bias voltages:

Table 88. | DDR Memory Bias Voltage Minimum/Maximum Values |

|

| ||

|

|

|

|

|

|

| Symbol | Parameter | Voltages | Units | |

|

|

| |||

|

|

| Minimum | Maximum |

|

|

|

|

|

|

|

| VCC25 | 2.5 V Supply Voltage | 2.3 | 2.7 | V |

| VREF | Memory I/O Reference Voltage | 1.15 | 1.35 | V |

| VTT | DDR Memory Termination Voltage | VREF - 0.04 | VREF + 0.04 | V |

For all registers relating to DRAM and other MCU related registers, see section 7.6, Table 149 of the Intel® 80321 I/O Processor Developer’s Manual.

5.2Components on the Peripheral Bus

The 80321 has a peripheral bus which contains the following peripheral devices:

•Flash ROM

•UART

•Rotary Switch

•Hex Display

Peripheral

All registers associated with the PBI can be found in the Intel® 80321 I/O Processor Developer’s Manual, section 8.6, table 128.

Board Manual | 71 |