Intel® IQ80321 I/O Processor Evaluation Platform

Software Reference

5.4.6Redboot Intel® IQ80321 DDR Memory Initialization Sequence

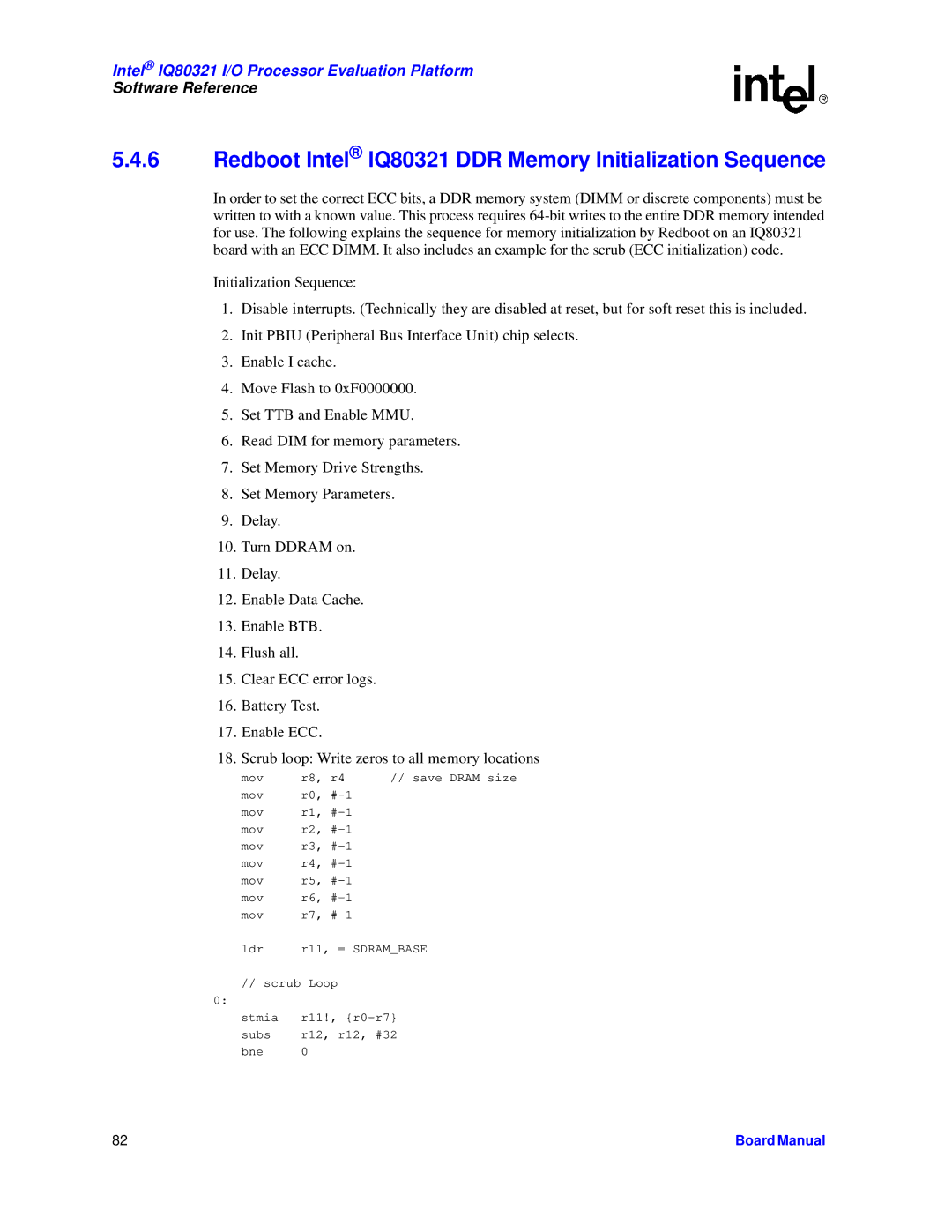

In order to set the correct ECC bits, a DDR memory system (DIMM or discrete components) must be written to with a known value. This process requires

Initialization Sequence:

1.Disable interrupts. (Technically they are disabled at reset, but for soft reset this is included.

2.Init PBIU (Peripheral Bus Interface Unit) chip selects.

3.Enable I cache.

4.Move Flash to 0xF0000000.

5.Set TTB and Enable MMU.

6.Read DIM for memory parameters.

7.Set Memory Drive Strengths.

8.Set Memory Parameters.

9.Delay.

10.Turn DDRAM on.

11.Delay.

12.Enable Data Cache.

13.Enable BTB.

14.Flush all.

15.Clear ECC error logs.

16.Battery Test.

17.Enable ECC.

18.Scrub loop: Write zeros to all memory locations

mov | r8, r4 | // save DRAM size |

mov | r0, |

|

mov | r1, |

|

mov | r2, |

|

mov | r3, |

|

mov | r4, |

|

mov | r5, |

|

mov | r6, |

|

mov | r7, |

|

ldr | r11, = SDRAM_BASE | |

// scrub Loop |

| |

0: |

|

|

stmia | r11!, | |

subs | r12, r12, #32 | |

bne | 0 |

|

82 | Board Manual |