Intel® IQ80321 I/O Processor Evaluation Platform

Hardware Reference Section

3.10.2PCIX Initialization Summary

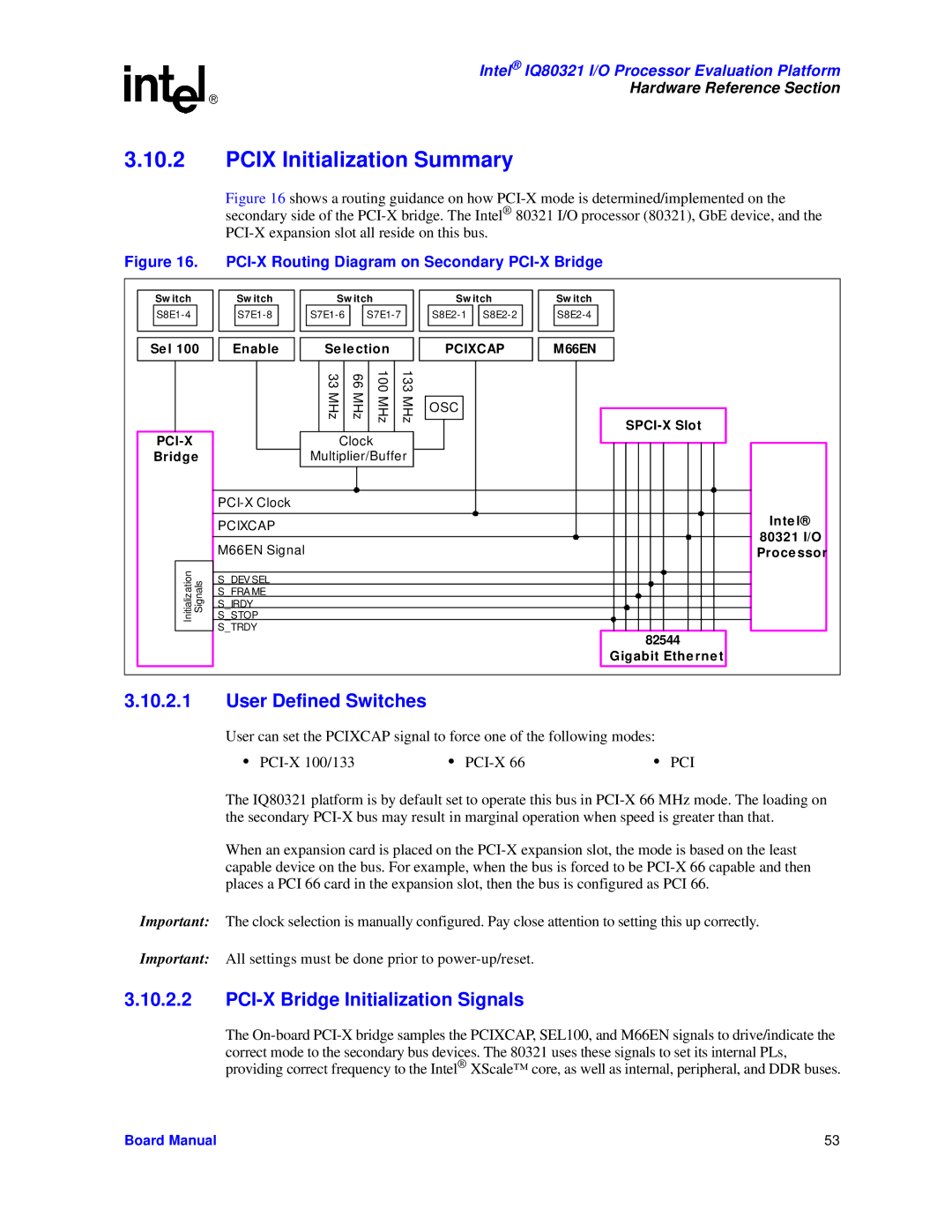

Figure 16 shows a routing guidance on how PCI-X mode is determined/implemented on the secondary side of the PCI-X bridge. The Intel® 80321 I/O processor (80321), GbE device, and the PCI-X expansion slot all reside on this bus.

Figure 16. PCI-X Routing Diagram on Secondary PCI-X Bridge

Sw itch |

| Sw itch | Sw itch |

| Sw itch | Sw itch | ||

|

| |||||||

Se l 100 | Enable | Se le ction |

| PCIXCAP | M66EN | |||

|

|

| 33 | 66 | 100 | 133 |

|

|

|

|

| MHz | MHz | MHz | MHz | OSC |

|

|

|

|

| |||||

|

|

|

|

|

|

|

| |

|

|

|

| Clock |

|

|

| |

Bridge |

| Multiplier/Buffer |

|

| ||||

|

|

|

|

|

|

|

| |

|

| PCIXCAP |

|

|

|

|

| Inte l® |

|

|

|

|

|

|

| 80321 I/O | |

|

| M66EN Signal |

|

|

|

|

| |

|

|

|

|

|

|

| Proce ssor | |

Initialization | Signals | S_DEV SEL |

|

|

|

|

|

|

S_FRA ME |

|

|

|

|

|

| ||

S_IRDY |

|

|

|

|

|

| ||

S_STOP |

|

|

|

|

|

| ||

S_TRDY |

|

|

|

|

|

| ||

|

|

|

|

|

|

| 82544 | |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| Gigabit Ethe rne t |

3.10.2.1User Defined Switches

User can set the PCIXCAP signal to force one of the following modes:

• | • | • PCI |

The IQ80321 platform is by default set to operate this bus in

When an expansion card is placed on the

Important: The clock selection is manually configured. Pay close attention to setting this up correctly.

Important: All settings must be done prior to

3.10.2.2PCI-X Bridge Initialization Signals

The

Board Manual | 53 |