Signals Reference

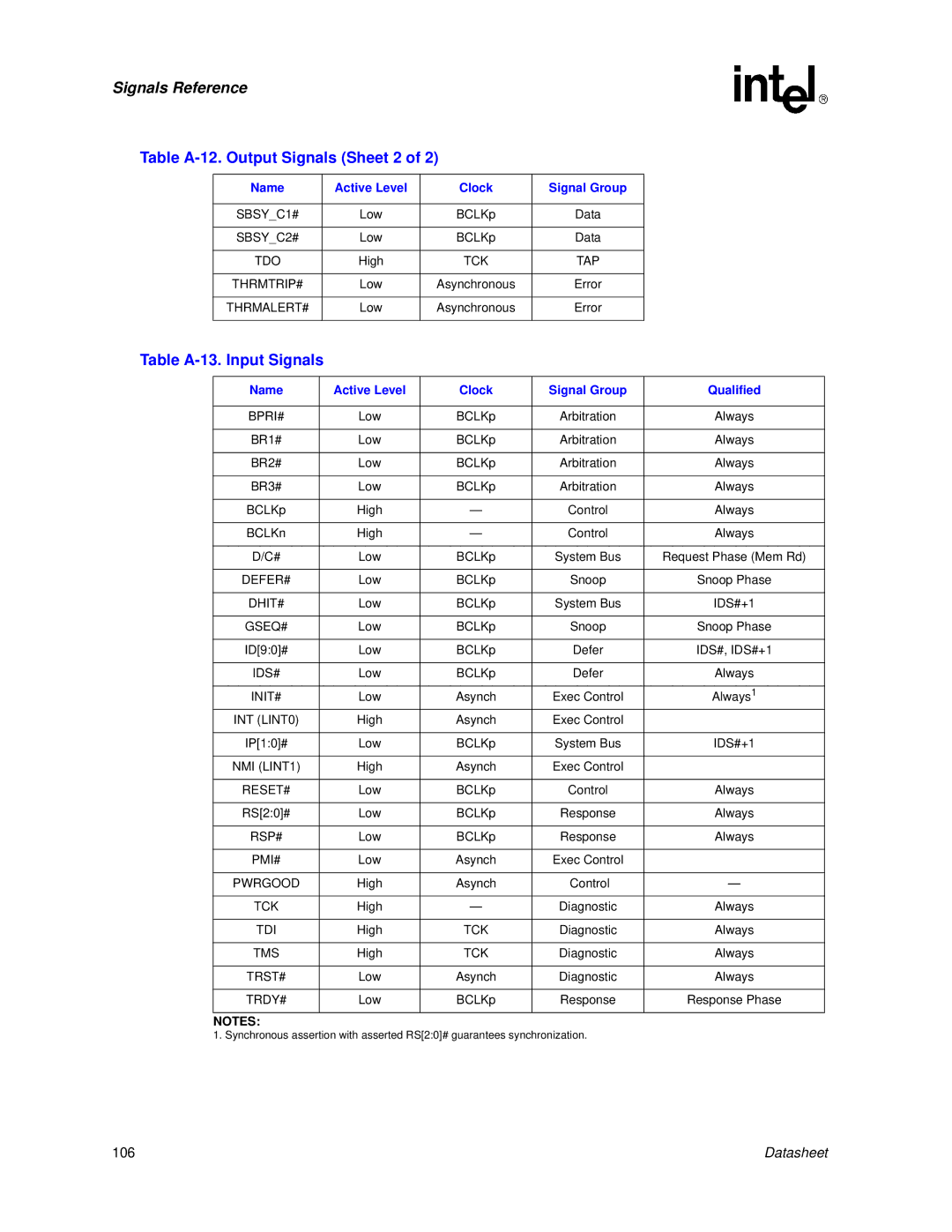

Table A-12. Output Signals (Sheet 2 of 2)

Name | Active Level | Clock | Signal Group |

|

|

|

|

SBSY_C1# | Low | BCLKp | Data |

|

|

|

|

SBSY_C2# | Low | BCLKp | Data |

|

|

|

|

TDO | High | TCK | TAP |

|

|

|

|

THRMTRIP# | Low | Asynchronous | Error |

|

|

|

|

THRMALERT# | Low | Asynchronous | Error |

|

|

|

|

Table A-13. Input Signals

Name | Active Level | Clock | Signal Group | Qualified |

|

|

|

|

|

BPRI# | Low | BCLKp | Arbitration | Always |

|

|

|

|

|

BR1# | Low | BCLKp | Arbitration | Always |

|

|

|

|

|

BR2# | Low | BCLKp | Arbitration | Always |

|

|

|

|

|

BR3# | Low | BCLKp | Arbitration | Always |

|

|

|

|

|

BCLKp | High | — | Control | Always |

|

|

|

|

|

BCLKn | High | — | Control | Always |

|

|

|

|

|

D/C# | Low | BCLKp | System Bus | Request Phase (Mem Rd) |

|

|

|

|

|

DEFER# | Low | BCLKp | Snoop | Snoop Phase |

|

|

|

|

|

DHIT# | Low | BCLKp | System Bus | IDS#+1 |

|

|

|

|

|

GSEQ# | Low | BCLKp | Snoop | Snoop Phase |

|

|

|

|

|

ID[9:0]# | Low | BCLKp | Defer | IDS#, IDS#+1 |

|

|

|

|

|

IDS# | Low | BCLKp | Defer | Always |

|

|

|

|

|

INIT# | Low | Asynch | Exec Control | Always1 |

INT (LINT0) | High | Asynch | Exec Control |

|

|

|

|

|

|

IP[1:0]# | Low | BCLKp | System Bus | IDS#+1 |

|

|

|

|

|

NMI (LINT1) | High | Asynch | Exec Control |

|

|

|

|

|

|

RESET# | Low | BCLKp | Control | Always |

|

|

|

|

|

RS[2:0]# | Low | BCLKp | Response | Always |

|

|

|

|

|

RSP# | Low | BCLKp | Response | Always |

|

|

|

|

|

PMI# | Low | Asynch | Exec Control |

|

|

|

|

|

|

PWRGOOD | High | Asynch | Control | — |

|

|

|

|

|

TCK | High | — | Diagnostic | Always |

|

|

|

|

|

TDI | High | TCK | Diagnostic | Always |

|

|

|

|

|

TMS | High | TCK | Diagnostic | Always |

|

|

|

|

|

TRST# | Low | Asynch | Diagnostic | Always |

|

|

|

|

|

TRDY# | Low | BCLKp | Response | Response Phase |

|

|

|

|

|

NOTES:

1. Synchronous assertion with asserted RS[2:0]# guarantees synchronization.

106 | Datasheet |