Signals Reference

A.1.39 | IGNNE# (I) |

|

| |

| IGNNE# is ignored in the Itanium 2 processor system environment. | |||

A.1.40 | INIT# (I) |

|

| |

| The Initialization (INIT#) signal triggers an unmasked interrupt to the processor. INIT# is usually | |||

| used to break into hanging or idle processor states. Semantics required for platform compatibility | |||

| are supplied in the PAL firmware interrupt service routine. | |||

A.1.41 | INT (I) |

|

| |

| INT is the | |||

| been generated. The interrupt is maskable. The processor vectors to the interrupt handler after the | |||

| current instruction execution has been completed. An interrupt acknowledge transaction is | |||

| generated by the processor to obtain the interrupt vector from the interrupt controller. | |||

| The LINT[0] pin can be software configured to be used either as the INT signal or another local | |||

| interrupt. |

|

| |

A.1.42 | IP[1:0]# (I) |

|

| |

| The ID Parity (IP[1:0]#) signals are driven on the second clock of the Deferred Phase by the | |||

| deferring agent. IP0# protects the IDa[9:0]# and IDS# signals for the first clock, and IP[1]# | |||

| protects the IDb[9:2, 0]# and IDS# signals on the second clock. | |||

A.1.43 | LEN[2:0]# (I/O) |

|

| |

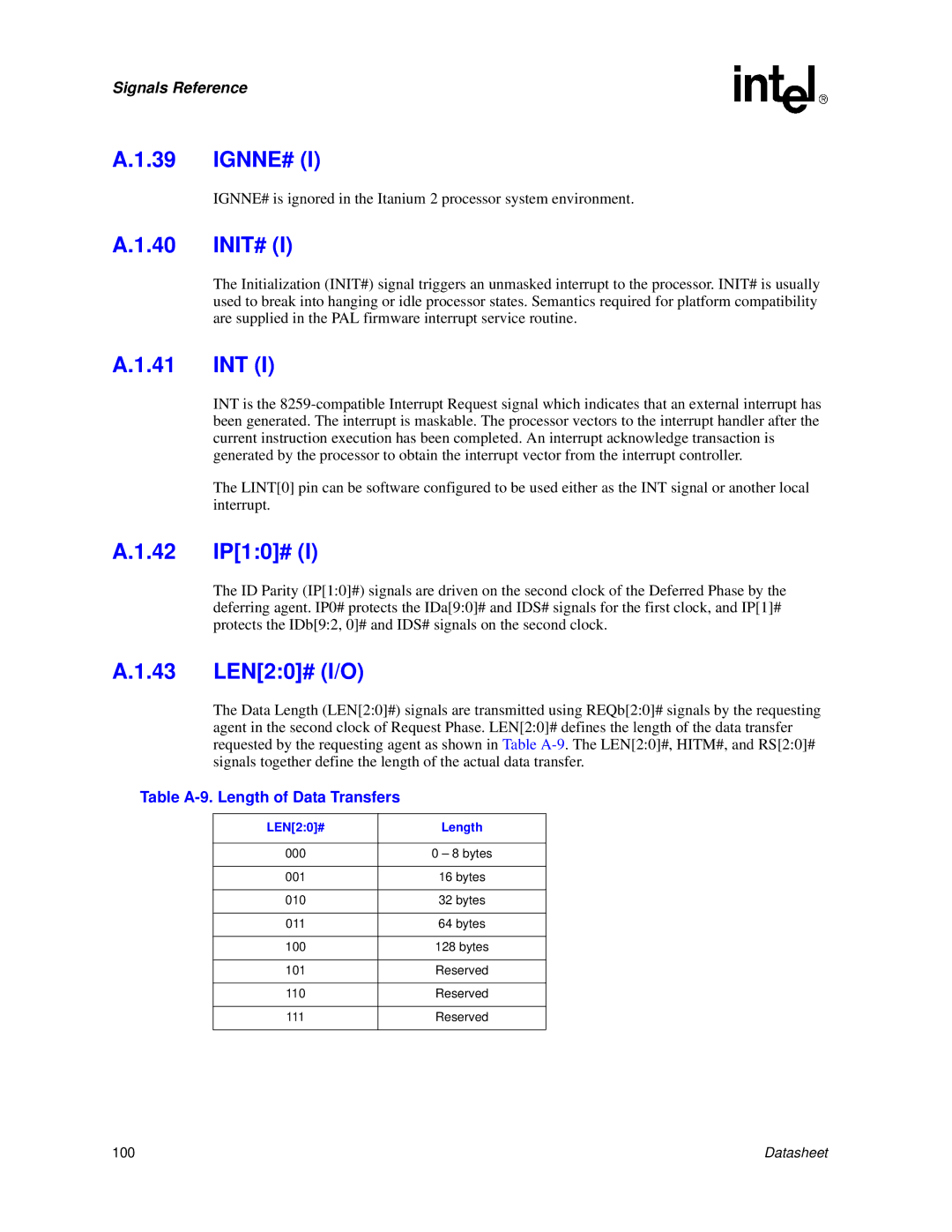

| The Data Length (LEN[2:0]#) signals are transmitted using REQb[2:0]# signals by the requesting | |||

| agent in the second clock of Request Phase. LEN[2:0]# defines the length of the data transfer | |||

| requested by the requesting agent as shown in Table | |||

| signals together define the length of the actual data transfer. | |||

Table |

|

| ||

|

|

|

|

|

| LEN[2:0]# |

| Length |

|

|

|

|

|

|

| 000 |

| 0 – 8 bytes |

|

|

|

|

|

|

| 001 |

| 16 bytes |

|

|

|

|

|

|

| 010 |

| 32 bytes |

|

|

|

|

|

|

| 011 |

| 64 bytes |

|

|

|

|

|

|

| 100 |

| 128 bytes |

|

|

|

|

|

|

| 101 |

| Reserved |

|

|

|

|

|

|

| 110 |

| Reserved |

|

|

|

|

|

|

| 111 |

| Reserved |

|

|

|

|

|

|

100 | Datasheet |