Signals Reference

For memory or I/O transactions, the

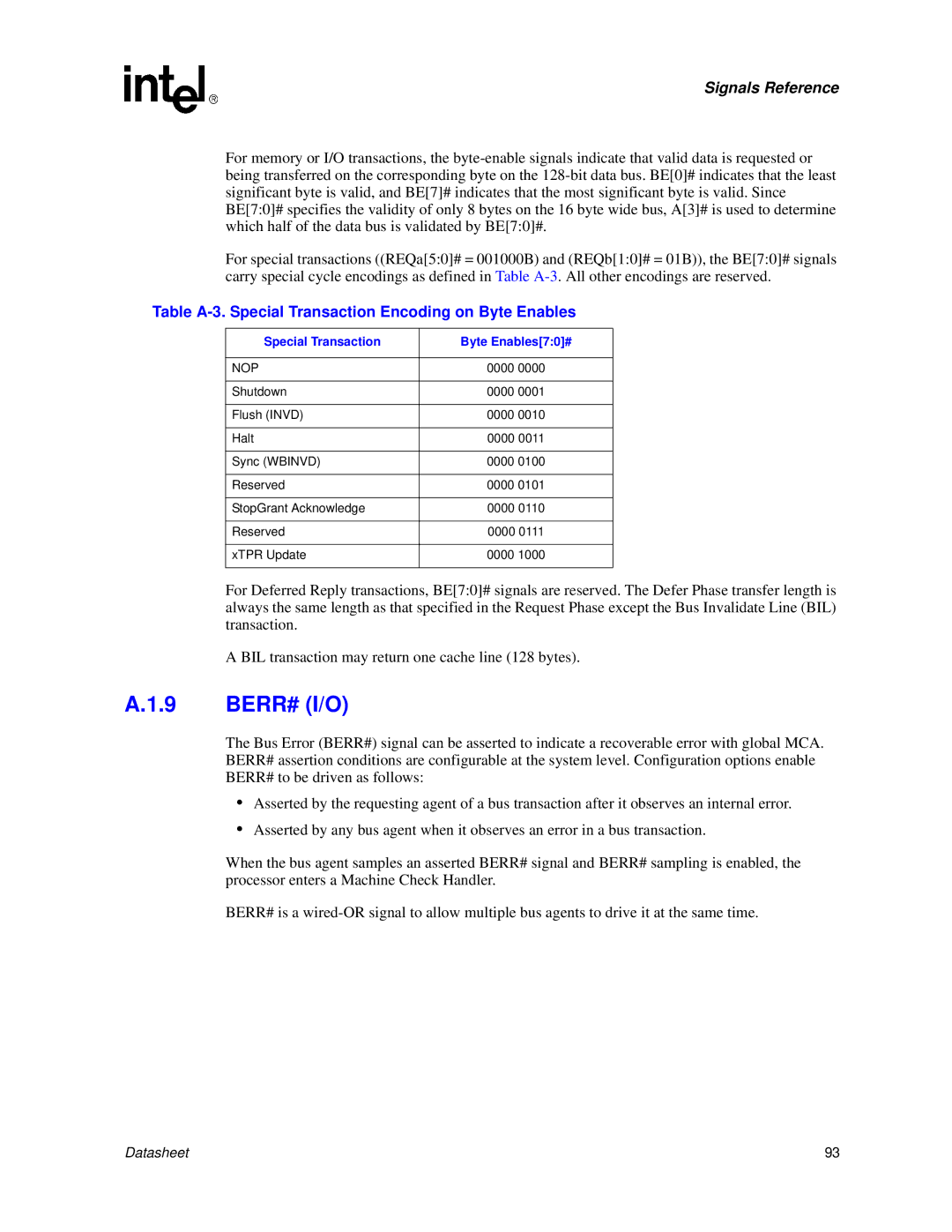

For special transactions ((REQa[5:0]# = 001000B) and (REQb[1:0]# = 01B)), the BE[7:0]# signals carry special cycle encodings as defined in Table

Table A-3. Special Transaction Encoding on Byte Enables

Special Transaction | Byte Enables[7:0]# |

|

|

NOP | 0000 0000 |

|

|

Shutdown | 0000 0001 |

|

|

Flush (INVD) | 0000 0010 |

|

|

Halt | 0000 0011 |

|

|

Sync (WBINVD) | 0000 0100 |

|

|

Reserved | 0000 0101 |

|

|

StopGrant Acknowledge | 0000 0110 |

|

|

Reserved | 0000 0111 |

|

|

xTPR Update | 0000 1000 |

|

|

For Deferred Reply transactions, BE[7:0]# signals are reserved. The Defer Phase transfer length is always the same length as that specified in the Request Phase except the Bus Invalidate Line (BIL) transaction.

A BIL transaction may return one cache line (128 bytes).

A.1.9 BERR# (I/O)

The Bus Error (BERR#) signal can be asserted to indicate a recoverable error with global MCA. BERR# assertion conditions are configurable at the system level. Configuration options enable BERR# to be driven as follows:

•Asserted by the requesting agent of a bus transaction after it observes an internal error.

•Asserted by any bus agent when it observes an error in a bus transaction.

When the bus agent samples an asserted BERR# signal and BERR# sampling is enabled, the processor enters a Machine Check Handler.

BERR# is a

Datasheet | 93 |