Signals Reference

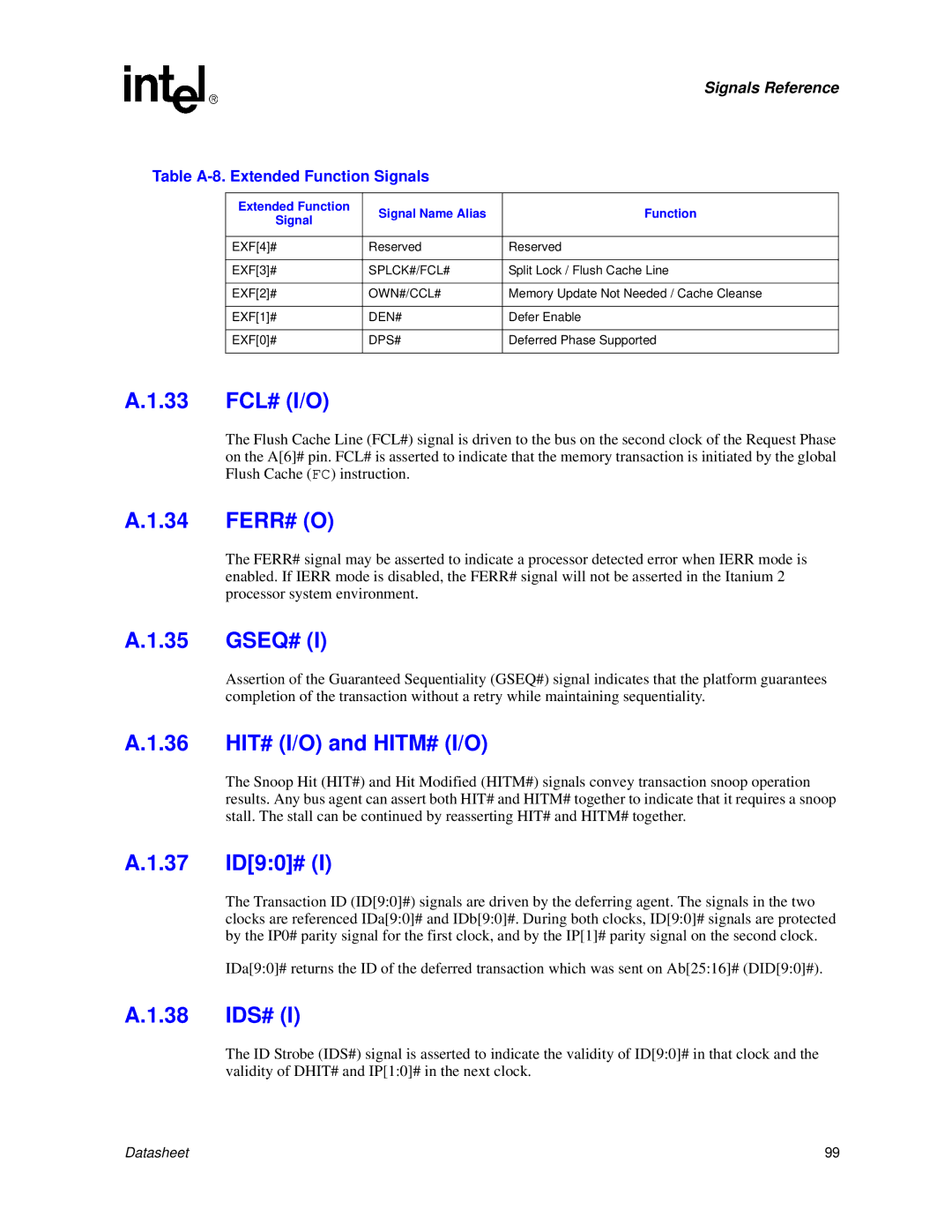

Table A-8. Extended Function Signals

Extended Function | Signal Name Alias | Function | |

Signal | |||

|

| ||

|

|

| |

EXF[4]# | Reserved | Reserved | |

|

|

| |

EXF[3]# | SPLCK#/FCL# | Split Lock / Flush Cache Line | |

|

|

| |

EXF[2]# | OWN#/CCL# | Memory Update Not Needed / Cache Cleanse | |

|

|

| |

EXF[1]# | DEN# | Defer Enable | |

|

|

| |

EXF[0]# | DPS# | Deferred Phase Supported | |

|

|

|

A.1.33 FCL# (I/O)

The Flush Cache Line (FCL#) signal is driven to the bus on the second clock of the Request Phase on the A[6]# pin. FCL# is asserted to indicate that the memory transaction is initiated by the global Flush Cache (FC) instruction.

A.1.34 FERR# (O)

The FERR# signal may be asserted to indicate a processor detected error when IERR mode is enabled. If IERR mode is disabled, the FERR# signal will not be asserted in the Itanium 2 processor system environment.

A.1.35 | GSEQ# (I) |

| Assertion of the Guaranteed Sequentiality (GSEQ#) signal indicates that the platform guarantees |

| completion of the transaction without a retry while maintaining sequentiality. |

A.1.36 | HIT# (I/O) and HITM# (I/O) |

| The Snoop Hit (HIT#) and Hit Modified (HITM#) signals convey transaction snoop operation |

| results. Any bus agent can assert both HIT# and HITM# together to indicate that it requires a snoop |

| stall. The stall can be continued by reasserting HIT# and HITM# together. |

A.1.37 | ID[9:0]# (I) |

| The Transaction ID (ID[9:0]#) signals are driven by the deferring agent. The signals in the two |

| clocks are referenced IDa[9:0]# and IDb[9:0]#. During both clocks, ID[9:0]# signals are protected |

| by the IP0# parity signal for the first clock, and by the IP[1]# parity signal on the second clock. |

| IDa[9:0]# returns the ID of the deferred transaction which was sent on Ab[25:16]# (DID[9:0]#). |

A.1.38 | IDS# (I) |

| The ID Strobe (IDS#) signal is asserted to indicate the validity of ID[9:0]# in that clock and the |

| validity of DHIT# and IP[1:0]# in the next clock. |

Datasheet | 99 |