6System Management Feature Specifications

The Itanium 2 processor includes a system management bus (SMBus) interface. This chapter describes the features of the SMBus and SMBus components.

6.1System Management Bus

6.1.1System Management Bus Interface

The Itanium 2 processor includes an Itanium processor family SMBus interface which allows access to several processor features. The system management components on the processor include two memory components (EEPROMs) and a thermal sensing device (digital thermometer). The processor information EEPROM (PIROM) is programmed by Intel with manufacturing and feature information specific to the Itanium 2 processor. This information is permanently

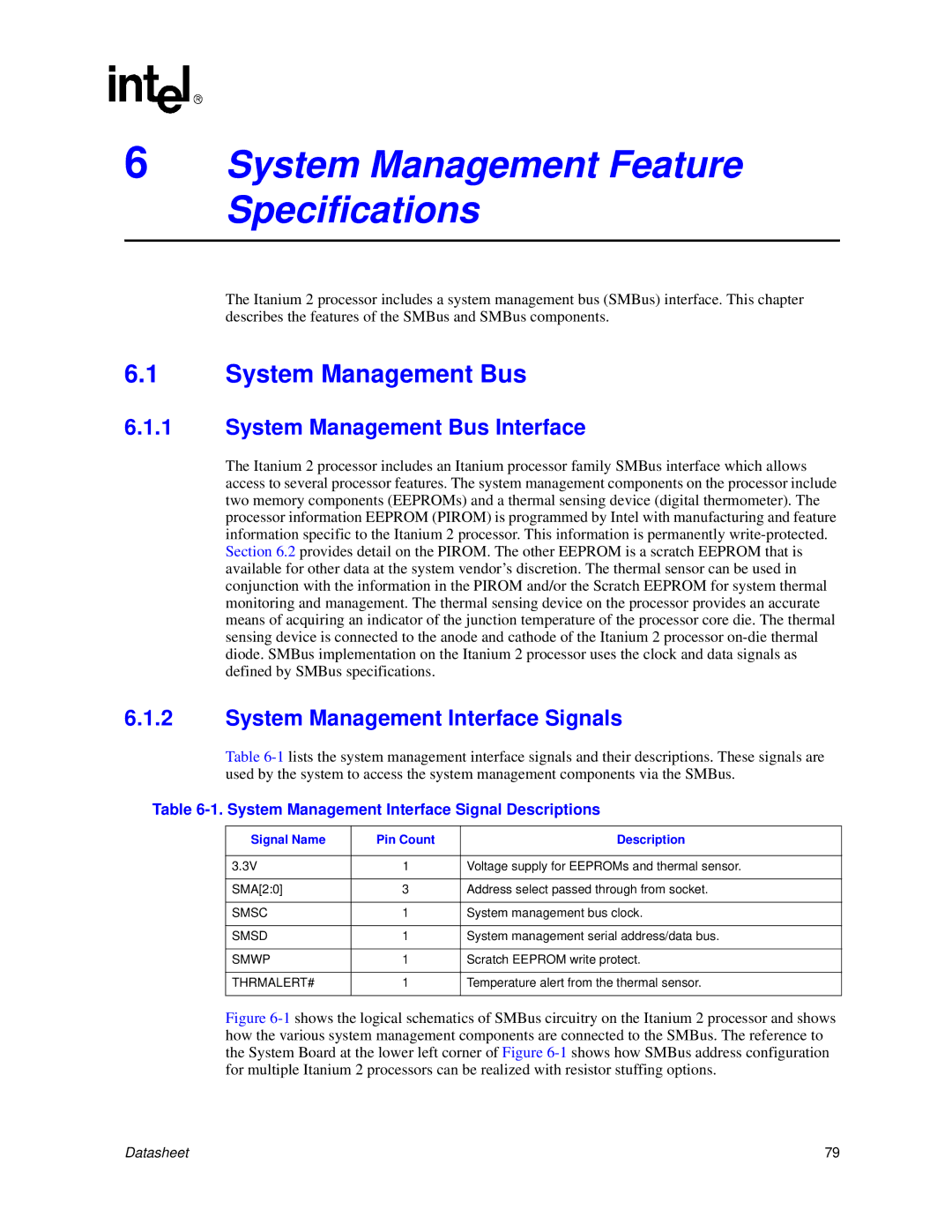

6.1.2System Management Interface Signals

Table

Table 6-1. System Management Interface Signal Descriptions

Signal Name | Pin Count | Description |

|

|

|

3.3V | 1 | Voltage supply for EEPROMs and thermal sensor. |

|

|

|

SMA[2:0] | 3 | Address select passed through from socket. |

|

|

|

SMSC | 1 | System management bus clock. |

|

|

|

SMSD | 1 | System management serial address/data bus. |

|

|

|

SMWP | 1 | Scratch EEPROM write protect. |

|

|

|

THRMALERT# | 1 | Temperature alert from the thermal sensor. |

|

|

|

Figure 6-1 shows the logical schematics of SMBus circuitry on the Itanium 2 processor and shows how the various system management components are connected to the SMBus. The reference to the System Board at the lower left corner of Figure 6-1 shows how SMBus address configuration for multiple Itanium 2 processors can be realized with resistor stuffing options.

Datasheet | 79 |