Electrical Specifications

Listed in Table

•The Itanium 2 processor 900 MHz with 1.5 MB L3 cache supports a bus ratio of 2/9.

•The Itanium 2 processor 1.0 GHz with 3 MB L3 cache supports a bus ratio of 2/10.

•The Itanium 2 processor 1.30 GHz with 3 MB L3 cache supports a bus ratio of 2/13.

•The Itanium 2 processor 1.40 GHz with 4 MB L3 cache supports a bus ratio of 2/14.

•The Itanium 2 processor 1.50 GHz with 6 MB L3 cache supports a bus ratio of 2/15.

•All other Itanium 2 processors will be locked at the correct supported ratios.

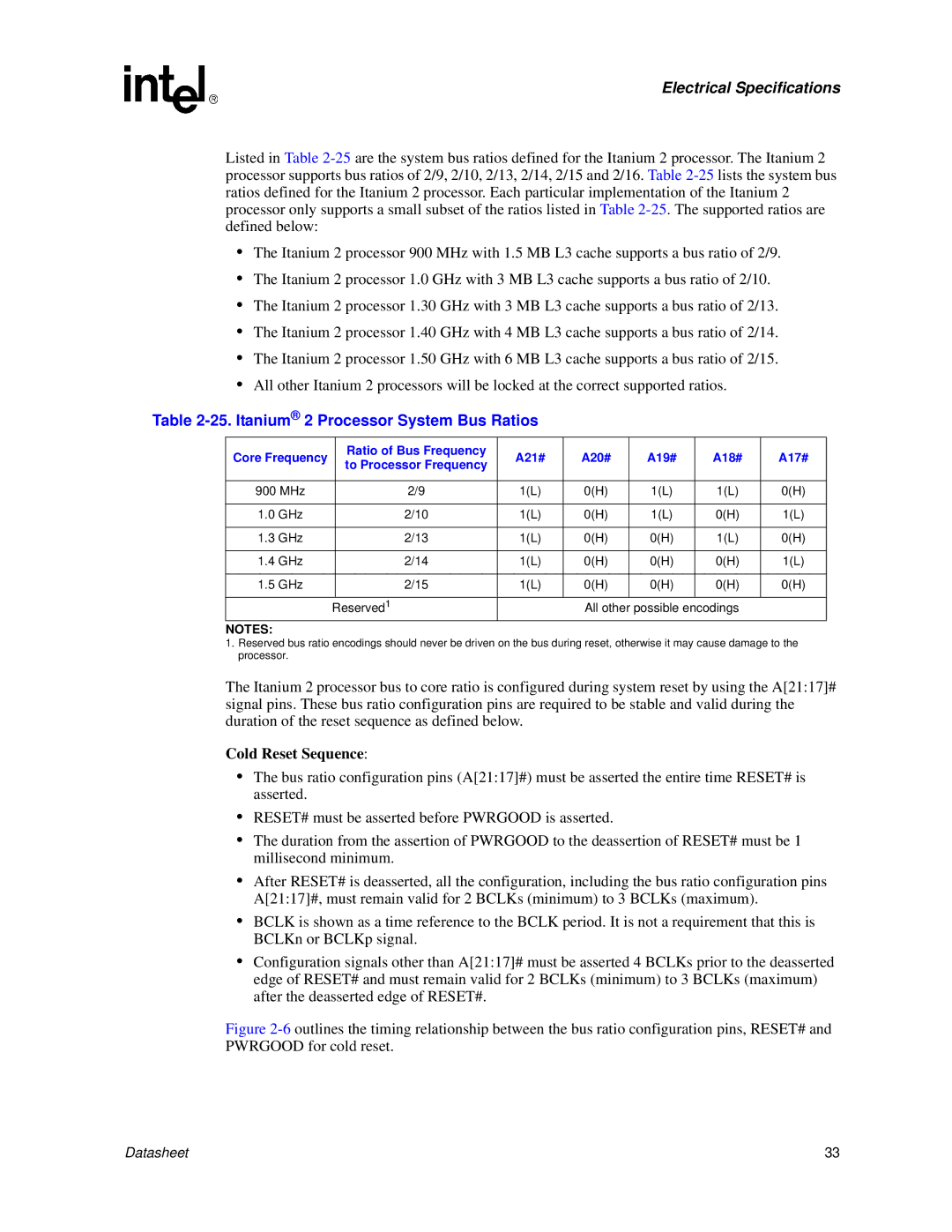

Table 2-25. Itanium® 2 Processor System Bus Ratios

Core Frequency |

| Ratio of Bus Frequency | A21# | A20# | A19# | A18# | A17# |

| to Processor Frequency | ||||||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

900 MHz |

| 2/9 | 1(L) | 0(H) | 1(L) | 1(L) | 0(H) |

|

|

|

|

|

|

|

|

1.0 GHz |

| 2/10 | 1(L) | 0(H) | 1(L) | 0(H) | 1(L) |

|

|

|

|

|

|

|

|

1.3 GHz |

| 2/13 | 1(L) | 0(H) | 0(H) | 1(L) | 0(H) |

|

|

|

|

|

|

|

|

1.4 GHz |

| 2/14 | 1(L) | 0(H) | 0(H) | 0(H) | 1(L) |

|

|

|

|

|

|

|

|

1.5 GHz |

| 2/15 | 1(L) | 0(H) | 0(H) | 0(H) | 0(H) |

|

|

|

|

|

|

|

|

|

| Reserved1 |

| All other possible encodings |

| ||

NOTES:

1.Reserved bus ratio encodings should never be driven on the bus during reset, otherwise it may cause damage to the processor.

The Itanium 2 processor bus to core ratio is configured during system reset by using the A[21:17]# signal pins. These bus ratio configuration pins are required to be stable and valid during the duration of the reset sequence as defined below.

Cold Reset Sequence:

•The bus ratio configuration pins (A[21:17]#) must be asserted the entire time RESET# is asserted.

•RESET# must be asserted before PWRGOOD is asserted.

•The duration from the assertion of PWRGOOD to the deassertion of RESET# must be 1 millisecond minimum.

•After RESET# is deasserted, all the configuration, including the bus ratio configuration pins A[21:17]#, must remain valid for 2 BCLKs (minimum) to 3 BCLKs (maximum).

•BCLK is shown as a time reference to the BCLK period. It is not a requirement that this is BCLKn or BCLKp signal.

•Configuration signals other than A[21:17]# must be asserted 4 BCLKs prior to the deasserted edge of RESET# and must remain valid for 2 BCLKs (minimum) to 3 BCLKs (maximum) after the deasserted edge of RESET#.

Figure 2-6 outlines the timing relationship between the bus ratio configuration pins, RESET# and PWRGOOD for cold reset.

Datasheet | 33 |