Electrical Specifications

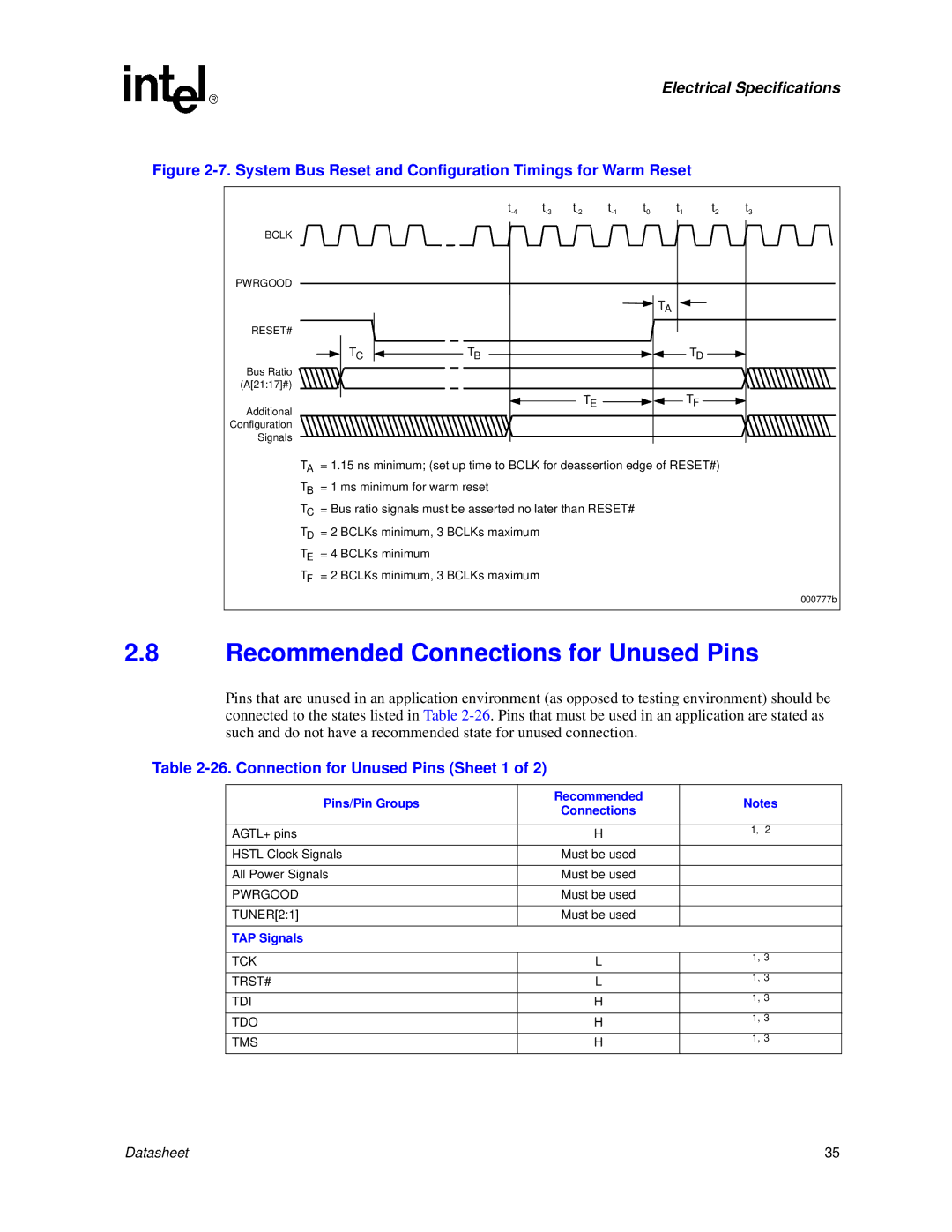

Figure 2-7. System Bus Reset and Configuration Timings for Warm Reset

| t0 | t1 | t2 | t3 | ||||

BCLK |

|

|

|

|

|

|

|

|

PWRGOOD |

|

|

|

|

|

|

|

|

|

|

|

|

|

| TA |

|

|

RESET# |

|

|

|

|

|

|

|

|

TC | TB |

|

|

|

|

| TD |

|

Bus Ratio |

|

|

|

|

|

|

|

|

(A[21:17]#) |

|

|

|

|

|

| TF |

|

Additional |

|

|

| TE |

|

|

| |

|

|

|

|

|

|

|

| |

Configuration |

|

|

|

|

|

|

|

|

Signals |

|

|

|

|

|

|

|

|

TA = 1.15 ns minimum; (set up time to BCLK for deassertion edge of RESET#)

TB = 1 ms minimum for warm reset

TC = Bus ratio signals must be asserted no later than RESET#

TD = 2 BCLKs minimum, 3 BCLKs maximum

TE = 4 BCLKs minimum

TF = 2 BCLKs minimum, 3 BCLKs maximum

000777b

2.8Recommended Connections for Unused Pins

Pins that are unused in an application environment (as opposed to testing environment) should be connected to the states listed in Table

Table 2-26. Connection for Unused Pins (Sheet 1 of 2)

Pins/Pin Groups | Recommended | Notes | |

Connections | |||

|

| ||

|

|

| |

AGTL+ pins | H | 1, 2 | |

|

|

| |

HSTL Clock Signals | Must be used |

| |

|

|

| |

All Power Signals | Must be used |

| |

|

|

| |

PWRGOOD | Must be used |

| |

|

|

| |

TUNER[2:1] | Must be used |

| |

|

|

| |

TAP Signals |

|

| |

|

|

| |

TCK | L | 1, 3 | |

|

|

| |

TRST# | L | 1, 3 | |

|

|

| |

TDI | H | 1, 3 | |

|

|

| |

TDO | H | 1, 3 | |

|

|

| |

TMS | H | 1, 3 | |

|

|

|

Datasheet | 35 |