Chapter 4

Chipset Features Setup

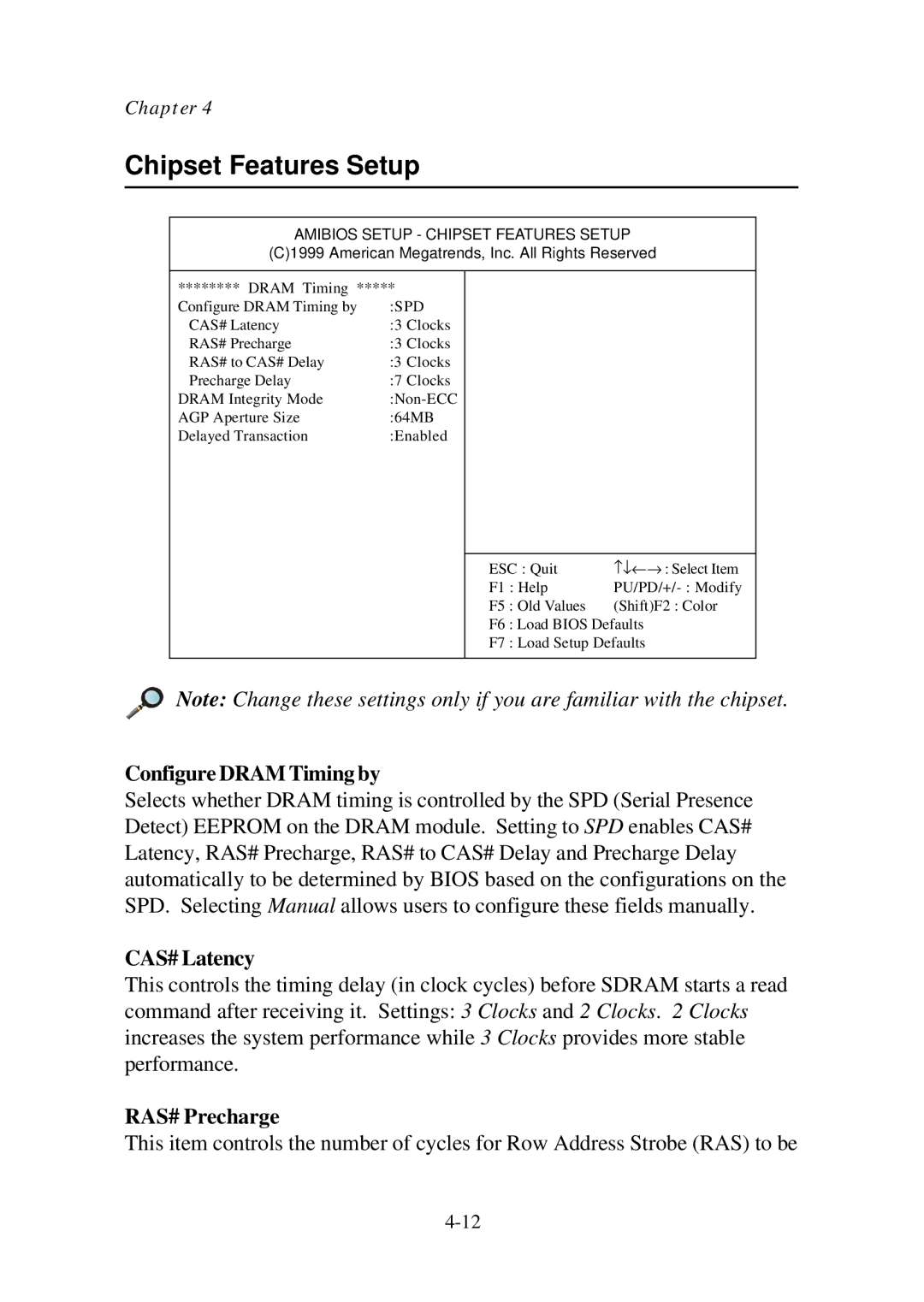

AMIBIOS SETUP - CHIPSET FEATURES SETUP

(C)1999 American Megatrends, Inc. All Rights Reserved

******** DRAM Timing *****

Configure DRAM Timing by | :SPD |

CAS# Latency | :3 Clocks |

RAS# Precharge | :3 Clocks |

RAS# to CAS# Delay | :3 Clocks |

Precharge Delay | :7 Clocks |

DRAM Integrity Mode | |

AGP Aperture Size | :64MB |

Delayed Transaction | :Enabled |

ESC : Quit | ↑↓←→ | : Select Item | |

F1 : Help | |||

F5 | : Old Values | (Shift)F2 : Color | |

F6 : Load BIOS Defaults |

| ||

F7 | : Load Setup Defaults |

| |

![]() Note: Change these settings only if you are familiar with the chipset.

Note: Change these settings only if you are familiar with the chipset.

Configure DRAM Timing by

Selects whether DRAM timing is controlled by the SPD (Serial Presence Detect) EEPROM on the DRAM module. Setting to SPD enables CAS# Latency, RAS# Precharge, RAS# to CAS# Delay and Precharge Delay automatically to be determined by BIOS based on the configurations on the SPD. Selecting Manual allows users to configure these fields manually.

CAS# Latency

This controls the timing delay (in clock cycles) before SDRAM starts a read command after receiving it. Settings: 3 Clocks and 2 Clocks. 2 Clocks increases the system performance while 3 Clocks provides more stable performance.

RAS# Precharge

This item controls the number of cycles for Row Address Strobe (RAS) to be