tecra m2 specifications

The Toshiba Tecra M2 is a versatile and robust laptop that was designed for business professionals and mobile users. Released in the early 2000s, this model earned a reputation for its reliability, performance, and build quality. It combines essential features that provide a seamless computing experience, making it an appealing choice for those seeking a portable yet capable device.One of the defining characteristics of the Tecra M2 is its lightweight design. Weighing in at approximately 4.5 pounds, the laptop is easy to carry, making it suitable for frequent travel. The sleek profile and durable chassis ensure that it withstands the rigors of daily use.

The Tecra M2 is equipped with a high-resolution 15-inch display, offering a comfortable viewing area for both work and multimedia tasks. With a resolution of up to 1400x1050 pixels, the screen delivers sharp images and vibrant colors, enhancing productivity during presentations or while editing documents.

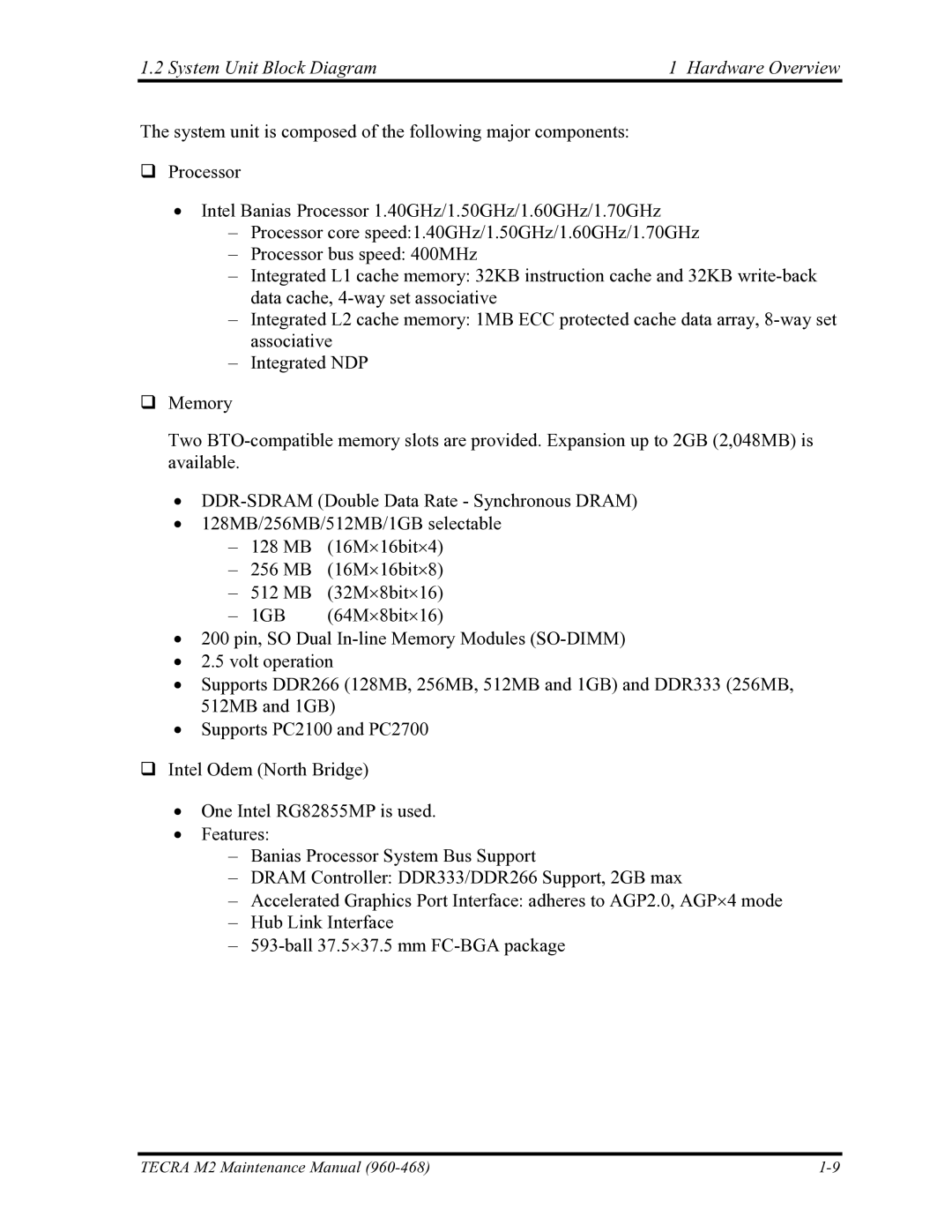

Powering the Tecra M2 is an Intel Pentium M processor, which helps to optimize battery life while providing sufficient performance for most business applications. This processor, combined with the laptop's up to 2GB of RAM, allows users to run multiple applications simultaneously without experiencing lag.

In terms of storage, the Tecra M2 supports a variety of configurations, including hard drives that range from 40GB to 80GB. This flexibility allows users to choose a setup that best fits their storage needs and usage patterns. Additionally, the laptop offers an optical drive for reading and writing CDs and DVDs, which was essential for data transfer and multimedia consumption during its time.

Connectivity is another strong point for the Tecra M2. It features multiple ports, including USB 2.0, Ethernet, and VGA, ensuring compatibility with a wide array of peripherals and networks. Wireless connectivity options such as Wi-Fi allow users to stay connected wherever they go, enhancing its appeal for mobile professionals.

The Tecra M2 is also designed with user comfort in mind. The keyboard is well-spaced and provides a satisfying tactile feedback, making typing efficient for extended periods. Its ergonomic design helps reduce strain on the hands, which is crucial for those who spend long hours working on their laptops.

In summary, the Toshiba Tecra M2 stands out for its combination of portability, performance, and durability. With its solid construction, respectable specifications, and a range of connectivity options, it addresses the needs of business users looking for a trustworthy computing solution during the early 2000s.